# **MVME3100 Single Board Computer**

# **Programmer's Reference**

6806800G37A

April 2008

© Copyright 2008 Emerson

All rights reserved.

#### **Trademarks**

Emerson, Business-Critical Continuity, Emerson Network Power and the Emerson Network Power logo are trademarks and service marks of Emerson Electric Co. © 2008 Emerson Electric Co.

All other trademarks are the property of their respective owners.

Intel<sup>®</sup> is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

$Microsoft^{\otimes}$ ,  $Windows^{\otimes}$  and  $Windows Me^{\otimes}$  are registered trademarks of Microsoft Corporation; and  $Windows XP^{\mathsf{TM}}$  is a trademark of Microsoft Corporation.

PICMG<sup>®</sup>, CompactPCI<sup>®</sup>, AdvancedTCA<sup>™</sup> and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI Industrial Computer Manufacturers Group.

UNIX® is a registered trademark of The Open Group in the United States and other countries.

#### **Notice**

While reasonable efforts have been made to assure the accuracy of this document, Emerson assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Emerson reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Emerson to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to a Emerson website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Emerson,

It is possible that this publication may contain reference to or information about Emerson products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Emerson intends to announce such Emerson products, programming, or services in your country.

## **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Emerson.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

#### **Contact Address**

Emerson Network Power - Embedded Computing 2900 South Diablo Way, Suite 190 Tempe, AZ 85282 USA

# **Contents**

| Ab | bout this Manual |                                              |      |  |

|----|------------------|----------------------------------------------|------|--|

| 1  | Boar             | rd Description and Memory Maps               | . 15 |  |

|    | 1.1              | Introduction                                 | . 15 |  |

|    | 1.2              | Overview                                     |      |  |

|    | 1.3              | Memory Maps                                  | 19   |  |

|    |                  | 1.3.1 Default Processor Memory Map           | 19   |  |

|    |                  | 1.3.2 MOTLoad's Processor Memory Map         | 19   |  |

|    |                  | 1.3.3 VME Memory Map                         | 20   |  |

|    |                  | 1.3.4 System I/O Memory Map                  | 20   |  |

|    |                  | 1.3.5 System Status Register                 | 22   |  |

|    |                  | 1.3.6 System Control Register                | 22   |  |

|    |                  | 1.3.7 System Indicator Register              | 23   |  |

|    |                  | 1.3.8 Flash Control/Status Register          | 24   |  |

|    |                  | 1.3.9 PCI Bus Status Registers               | 25   |  |

|    |                  | 1.3.10 Interrupt Detect Register             | 27   |  |

|    |                  | 1.3.11 Presence Detect Register              | 28   |  |

|    |                  | 1.3.12 PLD Revision Register                 | 28   |  |

|    |                  | 1.3.13 PLD Data Code Register                | 29   |  |

|    |                  | 1.3.14 Test Register 1                       | 29   |  |

|    |                  | 1.3.15 Test Register 2                       | 29   |  |

|    |                  | 1.3.16 External Timer Registers              | 30   |  |

|    |                  | 1.3.16.1 Prescalar Register                  | 30   |  |

|    |                  | 1.3.16.2 Control Registers                   | 30   |  |

|    |                  | 1.3.16.3 Compare Registers                   | 31   |  |

|    |                  | 1.3.16.4 Counter Registers                   | 32   |  |

|    |                  | 1.3.17 Geographical Address Register         | 32   |  |

| 2  | Prog             | gramming Details                             | 33   |  |

|    | 2.1              | Introduction                                 | 33   |  |

|    | 2.2              | MPC8540 Reset Configuration                  |      |  |

|    | 2.3              | MPC8540 Interrupt Controller                 |      |  |

|    | 2.4              | Local Bus Controller Chip Select Assignments |      |  |

|    | 2.5              | Two-Wire Serial Interface                    |      |  |

|    | 2.6              | User Configuration EEPROM                    |      |  |

|    | 2.7              | VPD EEPROM                                   |      |  |

|    | 2.8              | RTM VPD EEPROM                               |      |  |

|    | 2.9              | Ethernet PHY Address                         |      |  |

|    |                  | Flash Memory                                 |      |  |

|    | 2.10             | Tidon Monory                                 | 70   |  |

#### Contents

| 2.11 | PCI IDSEL Definition                                 | 41 |

|------|------------------------------------------------------|----|

|      | PCI Arbitration Assignments                          |    |

|      | Clock Distribution                                   |    |

| 2.14 | MPC8540 Real-Time Clock Input                        | 44 |

| 2.15 | MPC8540 LBC Clock Divisor                            | 44 |

| A.1  | Emerson Network Power - Embedded Computing Documents | 45 |

| A.2  | Manufacturers' Documents                             | 45 |

| A.3  | Related Specifications                               | 47 |

# List of Figures

| Figure 1-1 | Block Diagram | <br> | <br>16 |

|------------|---------------|------|------|------|------|------|------|------|--------|

# List of Tables

| Table 1-1  | MVME3100 Features Summary                               | . 16 |

|------------|---------------------------------------------------------|------|

| Table 1-2  | MVME712-101 RTM Features Summary                        | . 18 |

| Table 1-3  | Default Processor Address Map                           | . 19 |

| Table 1-4  | MOTLoad's Processor Address Map                         | . 19 |

| Table 1-5  | System I/O Memory Map                                   | . 20 |

| Table 1-6  | System Status Register                                  | . 22 |

| Table 1-7  | System Control Register                                 | . 22 |

| Table 1-8  | System Indicator Register                               |      |

| Table 1-9  | Flash Control/Status Register                           | . 24 |

| Table 1-10 | PCI Bus A Status Register                               | . 25 |

| Table 1-11 | PCI Bus B Status Register                               | . 25 |

| Table 1-12 | PCI Bus C Status Register                               | . 26 |

| Table 1-13 | Interrupt Detect Register                               | . 27 |

| Table 1-14 | Presence Detect Register                                | . 28 |

| Table 1-15 | PLD Revision Register                                   | . 28 |

| Table 1-16 | PLD Data Code Register                                  | . 29 |

| Table 1-17 | Test Register 1                                         | . 29 |

| Table 1-18 | Test Register 2                                         | . 29 |

| Table 1-19 | Prescalar Register                                      | . 30 |

| Table 1-20 | Tick Timer Control Registers                            | . 30 |

| Table 1-21 | Tick Timer Compare Registers                            | . 32 |

| Table 1-22 | Tick Timer Counter Registers                            | . 32 |

| Table 2-1  | MPC8540 Power-on Reset Configuration Settings           | . 33 |

| Table 2-2  | MPC8540 Interrupt Controller                            | . 37 |

| Table 2-3  | LBC Chip Select Assignments                             | . 38 |

| Table 2-4  | I2C Bus Device Addressing                               | . 38 |

| Table 2-5  | PHY Types and MII Management Bus Addresses              | . 40 |

| Table 2-6  | Flash Options                                           | . 40 |

| Table 2-7  | IDSEL and Interrupt Mapping for PCI Devices             | . 41 |

| Table 2-8  | Planar PCI Device Identification                        | . 42 |

| Table 2-9  | PCI Arbitration Assignments                             | . 43 |

| Table 2-10 | Clock Assignments                                       | . 43 |

| Table A-1  | Emerson Network Power - Embedded Computing Publications | . 45 |

| Table A-2  | Manufacturers' Documents                                | . 45 |

| Table A-3  | Related Specifications                                  |      |

# About this Manual

# **Overview of Contents**

This manual is divided into the following chapters and appendices:

Chapter 1, *Board Description and Memory Maps*, provides a brief product description and a block diagram. The remainder of the chapter provides information on memory maps and system and configuration registers.

Chapter 2, *Programming Details*, provides additional programming information including IDSEL mapping, interrupt assignments for the MPC8540 interrupt controller, Flash memory, two-wire serial interface addressing, and other device and system considerations.

Appendix A, *Related Documentation*, provides a listing of related Emerson manuals, vendor documentation, and industry specifications.

# **Abbreviations**

| Abbreviation | Description                                       |

|--------------|---------------------------------------------------|

| ATA          | Advanced Technology Attachment                    |

| CHRP         | Common Hardware Reference Platform                |

| CMC          | Common Mezzanine Card                             |

| COM          | Communication                                     |

| CPU          | Central Processing Unit                           |

| DDR          | Double Data Rate                                  |

| DMA          | Direct Memory Access                              |

| DRAM         | Dynamic Random Access Memory                      |

| ECC          | Error Correction Code                             |

| FIFO         | First In First Out                                |

| GA           | General Availability                              |

| GMII         | Gigabit Media Independent Interface               |

| GPCM         | General Purpose Chip select Machine               |

| I/O          | Input/Output                                      |

| IEEE         | Institute of Electrical and Electronics Engineers |

| KB           | Kilobytes                                         |

| LBC          | Local Bus Controller                              |

| LED          | Light Emitting Diode                              |

| MB           | Megabyte                                          |

| MHz          | Megahertz                                         |

| MIIM         | MII Management                                    |

| NVRAM        | Non Volatile RAM                                  |

| PCI          | Peripheral Connect Interface                      |

| PCI-X        | Peripheral Component Interconnect -X              |

| PHY          | Physical Layer                                    |

| PIC          | Programmable Interrupt Controller                 |

| PIM          | PCI Mezzanine Card Input/Output Module            |

| PLD          | Programmable Logic Device                         |

| PMC          | PCI Mezzanine Card (IEEE P1386.1)                 |

| POR          | Power-On Reset                                    |

| PReP         | PowerPC Reference Platform                        |

| PrPMC        | Processor PMC                                     |

| QUART        | Quad Universal Asynchronous Receiver/Transmitter  |

| R/W          | Read/Write                                        |

| RAM          | Random Access Memory                              |

| Abbreviation | Description                                 |

|--------------|---------------------------------------------|

| ROM          | Read Only Memory                            |

| RTC          | Real Time Clock                             |

| RTM          | Rear Transition Module                      |

| RTOS         | Real Time Operating System                  |

| SATA         | Serial AT Attachment                        |

| SBC          | Single Board Computer                       |

| SDRAM        | Synchronous Dynamic Random Access Memory    |

| SIG          | Special Interest Group                      |

| SMT          | Surface Mount Technology                    |

| SPD          | Serial Presence Detect                      |

| TSEC         | Triple Speed Ethernet Controllers           |

| TSOP         | Thin Small Outline Package                  |

| UART         | Universal Asynchronous Receiver/Transmitter |

| UNIX         | UNIX operating system                       |

| USB          | Universal Serial Bus                        |

| VIO          | Input/Output Voltage                        |

| VITA         | VMEbus International Trade Association      |

| VME          | VersaModule Eurocard                        |

| VMEbus       | VersaModule Eurocard bus                    |

# **Conventions**

The following table describes the conventions used throughout this manual.

| Notation       | Description                                                                                                   |

|----------------|---------------------------------------------------------------------------------------------------------------|

| 0x00000000     | Typical notation for hexadecimal numbers (digits are 0 through F), for example used for addresses and offsets |

| 0b0000         | Same for binary numbers (digits are 0 and 1)                                                                  |

| bold           | Used to emphasize a word                                                                                      |

| Screen         | Used for on-screen output and code related elements or commands in body text                                  |

| Courier + Bold | Used to characterize user input and to separate it from system output                                         |

| Reference      | Used for references and for table and figure descriptions                                                     |

| File > Exit    | Notation for selecting a submenu                                                                              |

| <text></text>  | Notation for variables and keys                                                                               |

| Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| [text]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Notation for software buttons to click on the screen and parameter description                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Repeated item for example node 1, node 2,, node 12                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Omission of information from example/command that is not necessary at the time being           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ranges, for example: 04 means one of the integers 0,1,2,3, and 4 (used in registers)           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Logical OR                                                                                     |

| ▲ WARNING  ××××××××××××××××××××××××××××××××××                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Indicates a hazardous situation which, if not avoided, could result in death or serious injury |

| ACAUTION  SOCIODOCIO DOCIODOCIO DOCIO DOCI | Indicates a hazardous situation which, if not avoided, may result in minor or moderate injury  |

| NOTICE  XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Indicates a property damage message                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No danger encountered. Pay attention to important information                                  |

# **Summary of Changes**

This manual has been revised and replaces all prior editions.

| Part Number | Publication Date | Description               |

|-------------|------------------|---------------------------|

| V3100A/PG1  |                  | First edition             |

| 6806800G37A | April 2008       | Updated to Emerson style. |

# **Comments and Suggestions**

We welcome and appreciate your comments on our documentation. We want to know what you think about our manuals and how we can make them better.

Mail comments to us by filling out the following online form: http://www.emersonnetworkpowerembeddedcomputing.com/ > Contact Us > Online Form

In "Area of Interest" select "Technical Documentation". Be sure to include the title, part number, and revision of the manual and tell us how you used it.

# 1.1 Introduction

This chapter briefly describes the board level hardware features of the MVME3100 single-board computer, including a table of features and a block diagram. The remainder of the chapter provides memory map information including a default memory map, MOTLoad's processor memory map, a default PCI memory map, MOTLoad's PCI memory map, system I/O memory map, and other configuration registers.

# 1.2 Overview

The MVME3100 is a single-slot, single-board computer based on the MPC8540 PowerQUICC III™ integrated processor. The MVME3100 provides serial ATA (sATA), USB 2.0, 2eSST VMEbus interfaces, dual 64-bit/100 MHz PMC sites, up to 256 MB of flash, dual 10/100/1000 Ethernet, one 10/100 Ethernet, and five serial ports. This board supports front and rear I/O and a single SODIMM module for DDR memory. Access to rear I/O is available with a rear transition module (RTM).

The MVME3100 Single-Board Computer Programmer's Reference provides general programming information, including memory maps, interrupts, and register data for the MVME3100 family of boards. This document should be used by anyone who wants general, as well as technical information about the MVME3100 products.

As of the printing date of this manual, the MVME3100 supports the models listed below.

| Model Number  | Description                                                                                                                                           |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MVME3100-1152 | 677 MHz MPC8540 PowerQUICC III <sup>™</sup> integrated processor, 256MB DDR SDRAM, 64MB flash, Gigabit Ethernet, SATA, IEEE handles                   |

| MVME3100-1263 | 833 MHz MPC8540 PowerQUICC III integrated processor, 512MB DDR SDRAM, 128MB flash, Gigabit Ethernet, SATA, USB, PCI expansion connector, IEEE handles |

| MVME721-101   | Rear Transition Module, direct connect, 75mm, PIM socket for PMC-1 I/O, four serial, 10/100/1000 Enet, 10/100 Enet                                    |

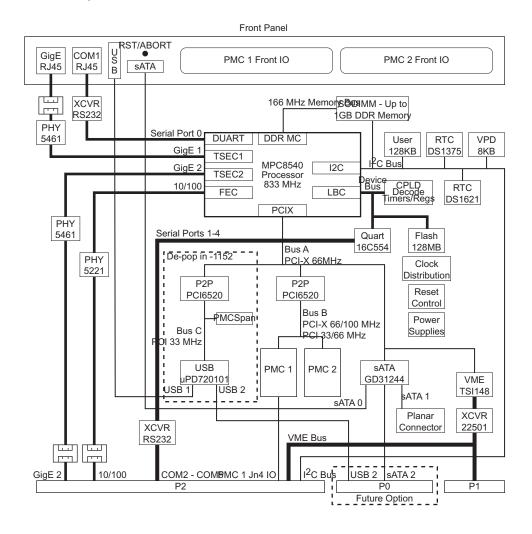

Figure 1-1 shows a block diagram of the MVME3100 and Table 1-1 lists the features of the MVME3100.

Figure 1-1 Block Diagram

Table 1-1 MVME3100 Features Summary

| Feature                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor/Host<br>Controller/Memory Controller | - Single 667/833 MHz MPC8540 PowerQUICC III™ integrated processor (e500 core) - Integrated 256KB L2 cache/SRAM - Integrated four-channel DMA controller - Integrated PCI/PCI-X controller - Two integrated 10/100/1000 Ethernet controllers - Integrated 10/100 Ethernet controller - Integrated dual UART - Integrated I2C controller - Integrated programmable interrupt controller - Integrated local bus controller - Integrated DDR SDRAM controller |

Table 1-1 MVME3100 Features Summary (continued)

| Feature             | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Memory       | <ul><li>One SODIMM socket</li><li>Up to DDR333, ECC</li><li>256MB or 512MB SODIMM</li></ul>                                                                                                                                                                                                                                                                                                                                       |

| I2C Interface       | <ul> <li>One 8KB VPD serial EEPROM</li> <li>Two 64KB user configuration serial EEPROMs</li> <li>One real-time clock (RTC) with removable battery</li> <li>One temperature sensor</li> <li>Interface to SPD(s) on SODIMM and P2 for RTM VPD</li> </ul>                                                                                                                                                                             |

| Flash               | - 32MB to 256MB soldered Flash with two alternate 1MB boot sectors selectable via a hardware switch     - Hardware switch or software bit write protection for entire logical bank                                                                                                                                                                                                                                                |

| PCI Interface       | Bus A:  - 66 MHz PCI-X (PCI-X 1.0b compliant)  - One TSi148 VMEbus controller  - One serial ATA (sATA) controller  - Two PCI6520 PCI-X-to-PCI-X bridges (primary side)                                                                                                                                                                                                                                                            |

|                     | Bus B:  - 33/66/100 MHz PCI/PCI-X (PCI 2.2 and PCI-X 1.0b compliant)  - Two +3.3V/5V selectable VIO, 64-bit, single-wide PMC sites or one double-wide PMC site (PrPMC ANSI/VITA 32-2003 and PCI-X Auxiliary ANSI/VITA 39-2003 compliant)  - One PCI6520 PCI-X-to-PCI-X bridge (secondary side)                                                                                                                                    |

|                     | Bus C (-1263 version):  - 33 MHz PCI (PCI 2.2 compliant)  - One USB 2.0 controller  - One PCI expansion connector for interface to PMCspan  - One PCI6520 PCI-X-to-PCI-X bridge (secondary side)                                                                                                                                                                                                                                  |

| I/O                 | One front panel RJ45 connector with integrated LEDs for front I/O: one serial channel One front panel RJ45 connector with integrated LEDs for front I/O: one 10/100/1000 Ethernet channel One front panel external sATA data connector for front I/O: one sATA channel One front panel USB Type A upright receptacle for front I/O: one USB 2.0 channel (-1263 version) PMC site 1 front I/O and rear P2 I/O PMC site 2 front I/O |

| Serial ATA          | <ul> <li>One four-channel sATA controller: one channel for front-panel I/O, one channel for planar I/O, one channel for future rear P0 I/O, and one channel is not used</li> <li>One planar data connector and one planar power connector for an interface to the sATA hard disk drive</li> </ul>                                                                                                                                 |

| USB (-1263 version) | <ul> <li>One four-channel USB 2.0 controller: one channel for front panel I/O<br/>and one channel for future rear P0 I/O. The other two channels are not<br/>used.</li> </ul>                                                                                                                                                                                                                                                     |

| Ethernet            | <ul> <li>Two 10/100/1000 MPC8540 Ethernet channels for front-panel I/O and rear P2 I/O</li> <li>One 10/100 MPC8540 Ethernet channel for rear P2 I/O</li> </ul>                                                                                                                                                                                                                                                                    |

Table 1-1 MVME3100 Features Summary (continued)

| Feature          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Interface | <ul> <li>One 16550-compatible, 9.6 to 115.2 KBAUD, MPC8540, asynchronous serial channel for front-panel I/O</li> <li>One quad UART controller to provide four 16550-compatible, 9.6 to 115.2 KBAUD, asynchronous serial channels for rear P2 I/O</li> </ul>                                                                                                                                                                                                                                             |

| Timers           | <ul><li>Four 32-bit MPC8540 timers</li><li>Four 32-bit timers in a PLD</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Watchdog Timer   | - One MPC8540 watchdog timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VME Interface    | <ul> <li>VME64 (ANSI/VITA 1-1994) compliant</li> <li>VME64 Extensions (ANSI/VITA 1.1-1997) compliant</li> <li>2eSST (ANSI/VITA 1.5-2003) compliant</li> <li>VITA 41.0, version 0.9 compliant</li> <li>Two five-row P1 and P2 backplane connectors</li> <li>One TSi148 VMEbus controller</li> </ul>                                                                                                                                                                                                      |

| Form Factor      | - Standard 6U VME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Miscellaneous    | <ul> <li>One front-panel reset/abort switch</li> <li>Four front-panel status indicators: 10/100/1000 Ethernet link/speed and activity, board fail, and user software controlled LED</li> <li>Six planar status indicators: one power supply status LED, two user software controlled LEDs, three sATA activity LEDs (one per channel)</li> <li>One standard 16-pin JTAG/COP header</li> <li>Boundary scan support</li> <li>Switches for VME geographical addressing in a three-row backplane</li> </ul> |

| Software Support | VxWorks operating system     Linux operating system                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 1-2 MVME712-101 RTM Features Summary

| Feature       | Description                                                                                                                                                                                                                                                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/0           | One five-row P2 backplane connector for serial and Ethernet I/O passed from the MVME3100     Four RJ-45 connectors for rear-panel I/O: four asynchronous serial channels     Two RJ-45 connectors with integrated LEDs for rear panel I/O: one 10/100/1000 Ethernet channel and one 10/100 Ethernet channel     One PIM site with rear-panel I/O |

| Miscellaneous | <ul> <li>Four rear-panel status indicators: 10/100/1000 and 10/100</li> <li>Ethernet link/speed and activity LEDs</li> </ul>                                                                                                                                                                                                                     |

# 1.3 Memory Maps

### 1.3.1 Default Processor Memory Map

The MPC8540 presents a default processor memory map following RESET negation. The following table shows the default memory map from the point of view of the processor. The e500 core only provides one default TLB entry to access boot code and it allows for accesses within the highest 4KB of memory. To access the full 8MB of default boot space (and the 1MB of CCSR space), additional TLB entries must be set up within the e500 core for mapping these regions. Refer to the MPC8540 Reference Manual listed in Appendix A, Related Documentation, for details.

This is the default location for the CCSRs, but it is not mapped after reset.

Table 1-3 Default Processor Address Map

| Processor Address |           |       |                       |       |

|-------------------|-----------|-------|-----------------------|-------|

| Start             | End       | Size  | Definition            | Notes |

| 0000 0000         | FF6F FFFF | 4087M | Not mapped            |       |

| FF70 0000         | FF7F FFFF | 1M    | MPC8540 CCS Registers | 1     |

| FF80 0000         | FFFF FFFF | 8M    | Flash                 | 2     |

Only FFFF F000 to FFFF FFFF is mapped after reset. The e500 core fetches the first instruction from FFFF FFFC following a reset.

## 1.3.2 MOTLoad's Processor Memory Map

MOTLoad's processor memory map is given in the following table.

Table 1-4 MOTLoad's Processor Address Map

| Processor Address |            |                        |                                                    |       |

|-------------------|------------|------------------------|----------------------------------------------------|-------|

| Start             | End        | Size                   | Definition                                         | Notes |

| 0000 0000         | top_dram-1 | dram_size<br>(2GB max) | System Memory (on-board DRAM)                      |       |

| 8000 0000         | DFFF FFFF  | 1.5GB                  | PCI Memory Space/VME                               |       |

| E000 0000         | E0FF FFFF  | 16MB                   | PCI I/O Space                                      |       |

| E100 0000         | E10F FFFF  | 1MB                    | MPC8540 CCSR                                       |       |

| E1100 0000        | E1FF FFFF  | 15MB                   | Not Used                                           |       |

| E200 0000         | E2FF FFFF  | 16MB                   | Status/Control Registers/UARTs,<br>External Timers |       |

| E300 0000         | EFFF FFFF  | 208MB                  | Not Used                                           |       |

| F000 0000         | F7FF FFFF  | 128MB                  | Reserved                                           | 1, 2  |

Table 1-4 MOTLoad's Processor Address Map (continued)

| Processor Address |           |                           |            |       |

|-------------------|-----------|---------------------------|------------|-------|

| Start             | End       | Size                      | Definition | Notes |

| bottom_flash      | FFFF FFFF | flash_size<br>(128MB max) | Flash      | 2     |

<sup>1.</sup> Reserved for future larger flash devices.

After RESET, the MPC8540 does not map any PCI memory space (inbound or outbound), and does not respond to Config cycles.

## 1.3.3 VME Memory Map

The MVME3100 is fully capable of supporting both the PReP and the CHRP VME Memory Map examples with RAM size limited to 2GB.

# 1.3.4 System I/O Memory Map

System resources including System Control and Status registers, external timers, and the QUART are mapped into a 16MB address range from the MVME3100 via the MPC8540 local bus controller (LBC). The memory map is defined in the following table, including the LBC bank chip select used to decode the register:

Table 1-5 System I/O Memory Map

| Address                  | Definition                    | LBC Bank /<br>Chip Select | Notes |

|--------------------------|-------------------------------|---------------------------|-------|

| E200 0000                | System Status Register        | 2                         | 3     |

| E200 0001                | System Control Register       | 2                         | 3     |

| E200 0002                | Status Indicator Register     | 2                         | 3     |

| E200 0003                | Flash Control/Status Register | 2                         | 3     |

| E200 0004                | PCI Bus A Status Register     | 2                         | 3     |

| E200 0005                | PCI Bus B Status Register     | 2                         | 3     |

| E200 0006                | PCI Bus C Status Register     | 2                         | 3     |

| E200 0007                | Interrupt Detect Register     | 2                         | 3     |

| E200 0008                | Presence Detect Register      | 2                         | 3     |

| E200 0009                | PLD Revision                  | 2                         | 3     |

| E200 000C                | PLD Date Code (32 bits)       | 2                         | 3     |

| E200 0010                | Test Register 1 (32 bits)     | 2                         | 3     |

| E200 0014                | Test Register 2 (32 bits)     | 2                         | 3     |

| E200 0018 -<br>E200 0FFF | Reserved                      |                           | 1     |

<sup>2.</sup> The flash is ligically one back but may be physically implemented in two banks.

Table 1-5 System I/O Memory Map (continued)

| Address                  | Definition                                 | LBC Bank /<br>Chip Select | Notes |

|--------------------------|--------------------------------------------|---------------------------|-------|

| E201 1000 -<br>E201 1FFF | COM 2 (QUART channel 1)                    | 3                         |       |

| E201 2000 -<br>E201 2FFF | COM 3 (QUART channel 2)                    | 3                         |       |

| E201 3000 -<br>E201 3FFF | COM 4 (QUART channel 3)                    | 3                         |       |

| E201 4000 -<br>E201 4FFF | COM 5 (QUART channel 4)                    | 3                         |       |

| E201 5000 -<br>E201 FFFF | Reserved                                   |                           | 1     |

| E202 0000                | External PLD Tick Timer Prescaler Register | 4                         | 2     |

| E202 0010                | External PLD Tick Timer 1 Control Register | 4                         | 2     |

| E202 0014                | External PLD Tick Timer 1 Compare Register | 4                         | 2     |

| E202 0018                | External PLD Tick Timer 1 Counter Register | 4                         | 2     |

| E202 001C                | Reserved                                   | 4                         | 2     |

| E202 0020                | External PLD Tick Timer 2 Control Register | 4                         | 2     |

| E202 0024                | External PLD Tick Timer 2 Compare Register | 4                         | 2     |

| E202 0028                | External PLD Tick Timer 2 Counter Register | 4                         | 2     |

| E202 002C                | Reserved                                   | 4                         | 2     |

| E202 0030                | External PLD Tick Timer 3 Control Register | 4                         | 2     |

| E202 0034                | External PLD Tick Timer 3 Compare Register | 4                         | 2     |

| E202 0038                | External PLD Tick Timer 3 Counter Register | 4                         | 2     |

| E202 003C                | Reserved                                   | 4                         | 2     |

| E202 0040                | External PLD Tick Timer 4 Control Register | 4                         | 2     |

| E202 0044                | External PLD Tick Timer 4 Compare Register | 4                         | 2     |

| E202 0048                | External PLD Tick Timer 4 Counter Register | 4                         | 2     |

| E202 004C -<br>E2FF FFFF | Reserved                                   |                           | 1     |

- 1. Reserved for future implementation

- 2. 32-bit write only

- 3. Byte read/write capable

#### 1.3.5 System Status Register

The MVME3100 board System Status register is a read-only register used to provide board status information.

Table 1-6 System Status Register

| REG   | System Status Register – 0xE2000000 |      |      |            |       |      |         |   |  |  |

|-------|-------------------------------------|------|------|------------|-------|------|---------|---|--|--|

| BIT   | 7                                   | 6    | 5    | 4          | 3     | 2    | 1       | 0 |  |  |

| FIELD | RSVD                                | RSVD | RSVD | SAFE_START | ABORT | RSVD | BD_TYPE |   |  |  |

| OPER  | R                                   |      |      |            |       |      |         |   |  |  |

| RESET | 0                                   | 0    | 0    | Х          | 0     | 0    | 0       | 0 |  |  |

BD\_TYPE

Board type. These bits indicate the board type.

00: VME SBC 01: PrPMC 10-11: Reserved

ABORT: This bit reflects the current state of the on-board abort signal. This is a debounced version of the abort switch and may be used to determine the state of the abort switch. A cleared condition indicates the abort switch is not depressed, while a set condition indicates the abort switch is asserted.

SAFE\_START: ENV safe start. This bit reflects the current state of the ENV safe start select switch. A set condition indicates that firmware should use the safe ENV settings. A cleared condition indicates that the ENV settings programmed in NVRAM should be used by the firmware.

RSVD: Reserved for future implementation.

# 1.3.6 System Control Register

The MVME3100 board System Control register provides board control bits.

Table 1-7 System Control Register

| REG | System C | System Control Register - 0xE2000001 |   |   |   |   |   |   |  |  |  |

|-----|----------|--------------------------------------|---|---|---|---|---|---|--|--|--|

| BIT | 7        | 6                                    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

**REG** System Control Register - 0xE2000001 **FIELD** EEPROM\_WP **ISTAT MASK** BD\_RESET RSVD RSVD RSVD R/W R R R R/W R/W **OPER** Χ RESET 0 0

Table 1-7 System Control Register (continued)

TSTAT\_MASK: Thermostat mask. This bit masks the DS1621 temperature sensor thermostat output. If this bit is cleared, the thermostat output is enabled to generate an interrupt. If the bit is set, the thermostat output is disabled from generating an interrupt.

EEPROM\_WPEEPROM: Write protect. This bit provides protection against inadvertent writes to the on-board EEPROM devices. Clearing this bit will enable writes to the EEPROM devices. Setting this bit write protects the devices. The devices are write protected following a reset.

BRD\_RST: Board reset. These bits force a hard reset of the board. If a pattern is written in bits 5-7 where bit 7 is set, bit 6 is cleared, and bit 5 is set (101), a hard reset is generated. Any other pattern written in bits 5-7, does not generate a hard reset. These bits are cleared automatically when the board reset has been completed. These bits are always cleared during a read.

RSVD: Reserved for future implementation.

# 1.3.7 System Indicator Register

The MVME3100 board provides a System Indicator register that may be read by the system software to determine the state of the on-board status indicator LEDs or written to by system software to illuminate the corresponding on-board LEDs.

Table 1-8 System Indicator Register

| REG   | System Indicator Register - 0xE2000002 |      |      |      |      |      |      |          |  |  |

|-------|----------------------------------------|------|------|------|------|------|------|----------|--|--|

| BIT   | 7                                      | 6    | 5    | 4    | 3    | 2    | 1    | 0        |  |  |

| FIELD | RSVD                                   | RSVD | RSVD | RSVD | USR3 | USR2 | USR1 | BRD_FAIL |  |  |

| OPER  | R                                      | R    | R    | R    | R/W  | R/W  | R/W  | R/W      |  |  |

| RESET | 0                                      | 0    | 0    | 0    | 0    | 0    | 0    | 1        |  |  |

BRD\_FAIL: Board fail. This bit controls the board fail LED located on the front panel. A set condition illuminates the front-panel LED and a cleared condition extinguishes the front-panel LED.

USR1\_LED: User LED 1. This bit controls the USR1 LED located on the front panel. A set condition illuminates the front-panel LED and a cleared condition extinguishes the front-panel LED.

USR2\_LED: User LED 2. This bit controls the planar USR2 LED. A set condition illuminates the LED and a cleared condition extinguishes the LED.

USR3\_LED: User LED 3. This bit controls the planar USR3 LED. A set condition illuminates the LED and a cleared condition extinguishes the LED.

RSVD: Reserved for future implementation.

### 1.3.8 Flash Control/Status Register

The MVME3100 provides software-controlled bank write protect and map select functions as well as boot block select, bank write protect, and activity status for the Flash.

| REG   | Flash | Flash Control/Status Register - 0xE2000003 |      |         |         |         |             |           |  |  |  |

|-------|-------|--------------------------------------------|------|---------|---------|---------|-------------|-----------|--|--|--|

| BIT   | 7     | 6                                          | 5    | 4       | 3       | 2       | 1           | 0         |  |  |  |

| FIELD | RSVD  | RSVD                                       | RSVD | MAP_SEL | F_WP_SW | F_WP_HW | FBT_BLK_SEL | FLASH_RDY |  |  |  |

| OPER  | R     | R                                          | R    | R/W     | R/W     | R       | R           | R         |  |  |  |

| RESET | 0     | 0                                          | 0    | 0       | 1       | Х       | Х           | 1         |  |  |  |

Table 1-9 Flash Control/Status Register

FLASH\_RDY: Flash ready. This bit provides the current state of the Flash devices' Ready/Busy# pins. These open drain output pins from each Flash device are wire OR'd to form Flash Ready.

FBT\_BLK\_SEL: Flash boot block select. This bit reflects the current state of the BOOT BLOCK B SELECT switch. A cleared condition indicates that boot block A is selected and mapped to the highest address. A set condition indicates that boot block B is selected and mapped to the highest address.

F\_WP\_HW: Hardware Flash bank write protect switch status. This bit reflects the current state of the FLASH BANK WP switch. A set condition indicates that the entire Flash bank is write protected. A cleared condition indicates that the Flash bank is not write protected.

F\_WP\_SW: Software Flash bank write protect. This bit provides software-controlled protection against inadvertent writes to the Flash memory devices. A set condition indicates that the entire Flash is write-protected. A cleared condition indicates that the Flash bank is not write-protected, only when the hardware write-protect bit is also not set. This bit is set during reset and must be cleared by the system software to enable writing of the Flash devices.

MAP\_SEL: Memory map select. When this bit is cleared, the Flash memory map is controlled by the Flash Boot Block Select switch. When the map select bit is set, boot block A is selected and mapped to the highest address.

RSVD: Reserved for future implementation.

#### 1.3.9 PCI Bus Status Registers

The PCI Bus Status registers provide PCI bus configuration information for each of the PCI buses.

Table 1-10 PCI Bus A Status Register

| REG   | PCI Bus A Status Register - 0xE2000004 |      |      |      |           |        |           |   |  |

|-------|----------------------------------------|------|------|------|-----------|--------|-----------|---|--|

| BIT   | 7                                      | 6    | 5    | 4    | 3         | 2      | 1         | 0 |  |

| FIELD | RSVD                                   | RSVD | RSVD | RSVD | PCI_A_64B | PCIX_A | PCI_A_SPD |   |  |

| OPER  | R                                      | R    | R    | R    | R         | R      | R         | R |  |

| RESET | 0                                      | 0    | 0    | 0    | 1         | Х      | 0         | 1 |  |

PCI\_A\_SPD

PCI bus A speed. Indicates the frequency of PCI bus A.

00: 33 MHz 01: 66 MHz 10: 100 MHz 11: 133 MHz

PCIX\_A: PCI-X bus A. A set condition indicates that bus A is operating in

PCI-X mode. A cleared condition indicates PCI mode.

PCI\_A\_64B: PCI bus A 64-bit. A set condition indicates that bus A is enabled to operate in 64-bit mode. A cleared condition indicates 32-bit mode.

RSVD: Reserved for future implementation.

Table 1-11 PCI Bus B Status Register

| REG   | PCI Bus B Status Register - 0xE2000005 |          |       |       |           |        |           |   |  |  |

|-------|----------------------------------------|----------|-------|-------|-----------|--------|-----------|---|--|--|

| BIT   | 7                                      | 6        | 5     | 4     | 3         | 2      | 1         | 0 |  |  |

| FIELD | 3.3V_VIO                               | 5.0V_VIO | ERDY2 | ERDY1 | PCl_B_64B | PCIX_B | PCI_B_SPD |   |  |  |

| OPER  | R                                      | R        | R     | R     | R         | R      | R         | R |  |  |

Table 1-11 PCI Bus B Status Register (continued)

| REG   | PCI Bus | PCI Bus B Status Register - 0xE2000005 |   |   |   |   |   |   |  |  |  |  |

|-------|---------|----------------------------------------|---|---|---|---|---|---|--|--|--|--|

| RESET | Χ       | X                                      | Х | 0 | 1 | Х | Х | Х |  |  |  |  |

#### PCI B SPD:

PCI bus B speed. Indicates the frequency of PCI bus B.

00: 33 MHz 01: 66 MHz 10: 100 MHz 11: 133 MHz

PCIX\_B: PCI-X bus B. A set condition indicates that bus B is operating in PCI-X mode. A cleared condition indicates PCI mode.

PCI\_B\_64B: PCI bus B 64-bit. A set condition indicates that bus B is enabled to operate in 64-bit mode. A cleared condition indicates 32-bit mode.

ERDY1: EREADY1. Indicates that the PrPMC module installed in PMC site 1 is ready for enumeration when set. If cleared, the PrPMC module is not ready for enumeration. If no PrPMC is installed, this bit is always set.

ERDY2: EREADY2. Indicates that the PrPMC module installed in PMC site 2 is ready for enumeration when set. If cleared, the PrPMC module is not ready for enumeration. If no PrPMC is installed, the bit is always set.

5.0V\_VIO: 5.0V VIO Enabled. This bit set indicates that the PMC bus (PCI bus B) is configured for 5.0V VIO.

3.3V\_VIO: 3.3V VIO enabled. This bit set indicates that the PMC bus (PCI bus B) is configured to 3.3V VIO.

Table 1-12 PCI Bus C Status Register

| REG   | PCI Bus C Status Register - 0xE2000006 |      |      |      |           |        |           |   |  |  |  |

|-------|----------------------------------------|------|------|------|-----------|--------|-----------|---|--|--|--|

| BIT   | 7                                      | 6    | 5    | 4    | 3         | 2      | 1         | 0 |  |  |  |

| FIELD | RSVD                                   | RSVD | RSVD | RSVD | PCI_C_64B | PCIX_C | PCI_C_SPD |   |  |  |  |

| OPER  | R                                      | R    | R    | R    | R         | R      | R         | R |  |  |  |

| RESET | X                                      | Х    | Х    | 0    | 1         | Х      | Х         | Х |  |  |  |

PCI\_C\_SPD:

PCI bus C speed. Indicates the frequency of PCI bus C.

00: 33 MHz 01: 66 MHz 10: 100 MHz 11: 133 MHz

PCIX\_C: PCI-X bus C. A set condition indicates that bus C is operating in PCI-X mode. A cleared condition indicates PCI mode.

PCI\_C\_64B: PCI bus C 64-bit. A set condition indicates that bus C is enabled to operate in 64-bit mode. A cleared condition indicates 32-bit mode.

RSVD: Reserved for future implementation.

#### 1.3.10 Interrupt Detect Register

The MVME3100 provides an Interrupt Detect register that may be read by the system software to determine which of the Ethernet PHYs originated their combined (OR'd) interrupt.

Table 1-13 Interrupt Detect Register

| REG   | Interrupt | Interrupt Detect Register - 0xE2000007 |      |      |      |         |           |           |  |  |  |  |

|-------|-----------|----------------------------------------|------|------|------|---------|-----------|-----------|--|--|--|--|

| BIT   | 7         | 6                                      | 5    | 4    | 3    | 2       | 1         | 0         |  |  |  |  |

| FIELD | RSVD      | RSVD                                   | RSVD | RSVD | RSVD | FEC_PHY | TSEC2_PHY | TSEC1_PHY |  |  |  |  |

| OPER  | R         | R                                      | R    | R    | R    | R       | R         | R         |  |  |  |  |

| RESET | 1         | 1                                      | 1    | 0    | 0    | 0       | 0         | 0         |  |  |  |  |

TSEC1\_PHY: TSEC1 PHY interrupt. If cleared, the TSEC1 interrupt is not asserted. If set, the TSEC1 interrupt is asserted.

TSEC2\_PHY: TSEC2 PHY interrupt. If cleared, the TSEC2 interrupt is not asserted. If set, the TSEC2 interrupt is asserted.

FEC\_PHY: FEC PHY interrupt. If cleared, the FEC interrupt is not asserted. If set, the FEC interrupt is asserted.

RSVD: Reserved for future implementation.

#### 1.3.11 Presence Detect Register

The MVME3100 provides a Presence Detect register that may be read by the system software to determine the presence of optional devices.

Table 1-14 Presence Detect Register

| REG   | Presence | Presence Detect Register - 0xE2000008 |      |      |      |     |       |       |  |  |  |

|-------|----------|---------------------------------------|------|------|------|-----|-------|-------|--|--|--|

| BIT   | 7        | 6                                     | 5    | 4    | 3    | 2   | 1     | 0     |  |  |  |

| FIELD | RSVD     | RSVD                                  | RSVD | RSVD | RSVD | PEP | PMC2P | PMC1P |  |  |  |

| OPER  | R        | R                                     | R    | R    | R    | R   | R     | R     |  |  |  |

| RESET | 0        | 0                                     | 0    | 0    | 0    | Х   | Х     | Х     |  |  |  |

PMC1P: PMC module 1 present. If cleared, there is no PMC module installed in site 1. If set, the PMC module is installed.

PMC2P: PMC module 2 present. If cleared, there is no PMC module installed in site 2. If set, the PMC module is installed.

PEP: PMCspan present. If cleared, there is no PMCspan module installed. If set, the PMCspan module is installed.

RSVD: Reserved for future implementation.

# 1.3.12 PLD Revision Register

The MVME3100 provides a PLD Revision register that may be read by the system software to determine the current revision of the timers/registers PLD.

Table 1-15 PLD Revision Register

| REG   | PLD Revi | PLD Revision Register - 0xE2000009 |   |   |   |   |   |   |  |  |  |

|-------|----------|------------------------------------|---|---|---|---|---|---|--|--|--|

| BIT   | 7        | 6                                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

| FIELD | PLD_RE\  | PLD_REV                            |   |   |   |   |   |   |  |  |  |

| OPER  | R        |                                    |   |   |   |   |   |   |  |  |  |

| RESET | 01       |                                    |   |   |   |   |   |   |  |  |  |

PLD\_REV: 8-bit field containing the current timer/register PLD revision. The revision number starts with 01.

#### 1.3.13 PLD Data Code Register