GLAST/LAT > DAQ and FSW > FSW > Doxygen Index > CTDB / V5-2-2

Constituent: sumt_bc_sib Tag: rad750

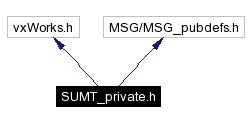

#include "vxWorks.h"

#include "MSG/MSG_pubdefs.h"

Include dependency graph for SUMT_private.h:

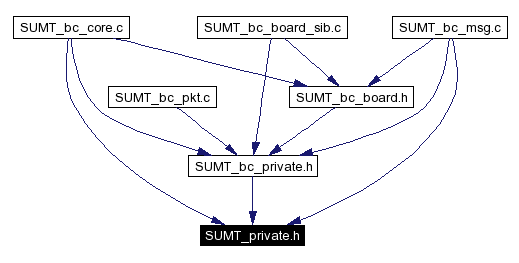

This graph shows which files directly or indirectly include this file:

Data Structures | |

| struct | _SUMT_Cmd_Blk |

| struct | _SUMT_Desc |

| struct | _SUMT_Log |

| struct | _SUMT_Regs |

REGISTER #0: SUMMIT Control Register Definitions | |

| #define | SUMT_XMTSW 0x0001 |

| #define | SUMT_INTEN 0x0002 |

| #define | SUMT_PPEN 0x0004 |

| #define | SUMT_DYNBC 0x0008 |

| #define | SUMT_BCEN 0x0010 |

| #define | SUMT_BUFR 0x0040 |

| #define | SUMT_ETCE 0x0400 |

| #define | SUMT_CHBEN 0x0800 |

| #define | SUMT_CHAEN 0x1000 |

| #define | SUMT_SRST 0x2000 |

| #define | SUMT_SBIT 0x4000 |

| #define | SUMT_STEX 0x8000 |

REGISTER #1: SUMMIT RT Status Register Definitions | |

| #define | SUMT_TERACT 0x0001 |

| #define | SUMT_READY 0x0002 |

| #define | SUMT_TPARF 0x0004 |

| #define | SUMT_EX 0x0008 |

| #define | SUMT_SSYSF 0x0010 |

| #define | SUMT_AUTOEN 0x0020 |

| #define | SUMT_LOCK 0x0040 |

| #define | SUMT_ABSTD 0x0080 |

| #define | SUMT_MSEL 0x0300 |

| #define | SUMT_RTPTY 0x0400 |

| #define | SUMT_RTA 0xf800 |

| #define | SUMT_MSEL_BC 0x0000 |

| #define | SUMT_MSEL_RT 0x0100 |

| #define | SUMT_MSEL_MT 0x0200 |

REGISTERS #s 3 AND 4: Interrupt Mask/Pending Definitions | |

| #define | SUMT_CBA 0x0002 |

| #define | SUMT_RTF 0x0004 |

| #define | SUMT_ILLOP 0x0008 |

| #define | SUMT_ILLCMD 0x0010 |

| #define | SUMT_EOL 0x0020 |

| #define | SUMT_ILCMD 0x0080 |

| #define | SUMT_IXEQ0 0x0100 |

| #define | SUMT_BDRCV 0x0200 |

| #define | SUMT_SUBAD 0x0400 |

| #define | SUMT_MERR 0x0800 |

| #define | SUMT_BITF 0x1000 |

| #define | SUMT_TAPF 0x2000 |

| #define | SUMT_WRAPF 0x4000 |

| #define | SUMT_DMAF 0x8000 |

REGISTER #6: BIT Word Definitions | |

| #define | SUMT_BIT_CHBF 0x0400 |

| #define | SUMT_BIT_CHAF 0x0800 |

| #define | SUMT_BIT_BITF 0x1000 |

| #define | SUMT_BIT_TAPF 0x2000 |

| #define | SUMT_BIT_WRAPF 0x4000 |

| #define | SUMT_BIT_DMAF 0x8000 |

REGISTER #9: Bus Status Word Register Definitions | |

| #define | SUMT_SWB_TF 0x0001 |

| #define | SUMT_SWB_SSYSF 0x0004 |

| #define | SUMT_SWB_BUSY 0x0008 |

| #define | SUMT_SWB_SRQ 0x0100 |

| #define | SUMT_SWB_INS 0x0200 |

| #define | SUMT_SWB_IMCLR 0x8000 |

Remote Terminal Message Information Word Definitions | |

| #define | SUMT_MIW_MAN 0x0001 |

| #define | SUMT_MIW_PRTY 0x0002 |

| #define | SUMT_MIW_OVR 0x0004 |

| #define | SUMT_MIW_TO 0x0008 |

| #define | SUMT_MIW_ILL 0x0010 |

| #define | SUMT_MIW_ME 0x0080 |

| #define | SUMT_MIW_RTRT 0x0100 |

| #define | SUMT_MIW_CHAB 0x0200 |

| #define | SUMT_MIW_WCMASK 0xf800 |

Remote Terminal Descriptor Definitions | |

| #define | SUMT_RT_CTRL_NII 0x0001 |

| #define | SUMT_RT_CTRL_BRD 0x0002 |

| #define | SUMT_RT_CTRL_AB 0x0004 |

| #define | SUMT_RT_CTRL_BAC 0x0010 |

| #define | SUMT_RT_CTRL_IBRD 0x0020 |

| #define | SUMT_RT_CTRL_IWA 0x0040 |

| #define | SUMT_RT_CTRL_INTX 0x0080 |

| #define | SUMT_RT_CTRL_INDEX 0xff00 |

Interrupt Information Word Defintions | |

| #define | SUMT_IIW_MBC 0x0001 |

| #define | SUMT_IIW_CBA 0x0002 |

| #define | SUMT_IIW_RTF 0x0004 |

| #define | SUMT_IIW_ILLOP 0x0008 |

| #define | SUMT_IIW_ILLCMD 0x0010 |

| #define | SUMT_IIW_EOL 0x0020 |

| #define | SUMT_IIW_ILCMD 0x0080 |

| #define | SUMT_IIW_IXEQ0 0x0100 |

| #define | SUMT_IIW_BDRCV 0x0200 |

| #define | SUMT_IIW_SUBAD 0x0400 |

| #define | SUMT_IIW_MERR 0x0800 |

Summit BC Control Word Values | |

| #define | SUMT_BC_OPCODE 0xf000 |

| #define | SUMT_BC_EOL 0x0000 |

| #define | SUMT_BC_SKIP 0x1000 |

| #define | SUMT_BC_EXE 0x4000 |

| #define | SUMT_BC_RTRY_1 0x0400 |

| #define | SUMT_BC_RTRY_2 0x0800 |

| #define | SUMT_BC_RTRY_3 0x0c00 |

| #define | SUMT_BC_RTRY_4 0x0000 |

| #define | SUMT_BC_CHA 0x0200 |

Summit Register Offsets | |

| #define | SUMT_REG_CONTROL 0x0000 |

| #define | SUMT_REG_STATUS 0x0002 |

| #define | SUMT_REG_COMMAND 0x0004 |

| #define | SUMT_REG_IRQ_MASK 0x0006 |

| #define | SUMT_REG_IRQ_PEND 0x0008 |

| #define | SUMT_REG_IRQ_LLP 0x000a |

| #define | SUMT_REG_BIT_WORD 0x000c |

| #define | SUMT_REG_TIME_TAG 0x000e |

| #define | SUMT_REG_SRT_DP 0x0010 |

| #define | SUMT_REG_STATUS_WORD 0x0012 |

| #define | SUMT_REG_I_RCV_0 0x0020 |

| #define | SUMT_REG_I_RCV_1 0x0022 |

| #define | SUMT_REG_I_XMT_0 0x0024 |

| #define | SUMT_REG_I_XMT_1 0x0026 |

| #define | SUMT_REG_IBRD_RCV_0 0x0028 |

| #define | SUMT_REG_IBRD_RCV_1 0x002a |

| #define | SUMT_REG_IBRD_XMT_0 0x002c |

| #define | SUMT_REG_IBRD_XMT_1 0x002e |

| #define | SUMT_REG_IMOD_RCV_0 0x0030 |

| #define | SUMT_REG_IMOD_RCV_1 0x0032 |

| #define | SUMT_REG_IMOD_XMT_0 0x0034 |

| #define | SUMT_REG_IMOD_XMT_1 0x0036 |

| #define | SUMT_REG_IMOD_BRD_RCV_0 0x0038 |

| #define | SUMT_REG_IMOD_BRD_RCV_1 0x003a |

| #define | SUMT_REG_IMOD_BRD_XMT_0 0x003c |

| #define | SUMT_REG_IMOD_BRD_XMT_1 0x003e |

Summit Register Write Bit Masks | |

| #define | SUMT_WMASK_CONTROL 0x9fff |

| #define | SUMT_WMASK_STATUS 0xff80 |

| #define | SUMT_WMASK_IRQ_MASK 0xffff |

| #define | SUMT_WMASK_IRQ_LLP 0xffff |

| #define | SUMT_WMASK_SRT_DP 0xffff |

| #define | SUMT_WMASK_ILL 0xffff |

Summit RT Descriptor Offsets | |

| #define | SUMT_DESC_SIZE 8 |

| #define | SUMT_DESC_CONTROL 0x0000 |

| #define | SUMT_DESC_DATA_A_PTR 0x0002 |

| #define | SUMT_DESC_DATA_B_PTR 0x0004 |

| #define | SUMT_DESC_BRDCAST_PTR 0x0006 |

Summit BC Command Block Offsets | |

| #define | SUMT_CMD_SIZE 16 |

| #define | SUMT_CMD_CONTROL 0x0000 |

| #define | SUMT_CMD_COMMAND_1 0x0002 |

| #define | SUMT_CMD_COMMAND_2 0x0004 |

| #define | SUMT_CMD_DATA_PTR 0x0006 |

| #define | SUMT_CMD_STATUS_1 0x0008 |

| #define | SUMT_CMD_STATUS_2 0x000a |

| #define | SUMT_CMD_BRANCH_ADDR 0x000c |

| #define | SUMT_CMD_TIME_DELAY 0x000e |

Summit Hardware Timing Values | |

| #define | SUMT_DELAY_RESET_HW 10000 |

| #define | SUMT_DELAY_RESET_SW 12000 |

| #define | SUMT_DELAY_BIT 2000000 |

| #define | SUMT_REG_RETRY 4 |

Device Access Macros | |

| #define | SUMT_WORD_READ(_base, _offset) SUMT_wordRead((_base), (_offset)) |

| #define | SUMT_WORD_WRITE(_base, _offset, _data) SUMT_wordWrite((_base), (_offset), (_data)) |

| #define | SUMT_REG_WRITE(_base, _offset, _data, _mask) SUMT_regWrite((_base), (_offset), (_data), (_mask)) |

Defines | |

| #define | SUMT_MSG(_status, _param) _msg_report((_status), 0, 1, (_param)) |

Typedefs | |

| typedef _SUMT_Regs | SUMT_Regs |

| typedef _SUMT_Desc | SUMT_Desc |

| typedef _SUMT_Cmd_Blk | SUMT_Cmd_Blk |

| typedef _SUMT_Log | SUMT_Log |

Functions | |

| unsigned short | SUMT_addrLocalToChip (unsigned int baseAddr, unsigned int localAddr) |

| Translate a CPU address into a Summit address. | |

| unsigned int | SUMT_addrChipToLocal (unsigned int baseAddr, unsigned short chipAddr) |

| Translate a Summit address into a CPU address. | |

| void | SUMT_memSet (unsigned int dest, unsigned short value, unsigned int numWords) |

| Set Summit shared memory to known value. | |

| void | SUMT_memCopyIn (void *dest, unsigned int src, unsigned int numWords) |

| Copy data from Summit shared memory. | |

| void | SUMT_memCopyOut (unsigned int dest, void *src, unsigned int numWords) |

| Copy data into Summit shared memory. | |

| unsigned short | SUMT_wordRead (unsigned int addr, unsigned int offset) |

| Synchronized read of Summit register or shared memory location. | |

| void | SUMT_wordWrite (unsigned int addr, unsigned int offset, unsigned short data) |

| Synchronized write to Summit register or shared memory location. | |

| void | SUMT_rtLegalize (unsigned short *regPair, unsigned short subAddr) |

| Create a Summit legalization mask. | |

| unsigned int | SUMT_reset (unsigned int regs) |

| Soft reset Summit controller hardware. | |

| unsigned int | SUMT_test (unsigned int regs) |

| Perform Summit controller hardware built in test. | |

| unsigned int | SUMT_regWrite (unsigned int addr, unsigned int offset, unsigned short data, unsigned short mask) |

| Write to a Summit controller register. | |

|

|

Indicates whether the device is using 1553 standard A (1) or standard B (1). |

|

|

Indicates the value of the device AUTOEN signal. |

|

|

Send command on bus channel A. |

|

|

End of command list; stop execution. |

|

|

Execute command and continue. |

|

|

Bit mask for accessing opcode value in control word. |

|

|

Retry command 1 time. |

|

|

Retry command 2 times. |

|

|

Retry command 3 times. |

|

|

Retry command 4 times. |

|

|

Skip command and implement time delay. |

|

|

Enables reception of broadcast messages on RT address '31'. |

|

|

Broadcast command received interrupt (RT only). |

|

|

General built-in self test failure. |

|

|

BIT channel A failure. |

|

|

BIT channel B failure. |

|

|

Device DMA failure. |

|

|

Terminal address parity failure. |

|

|

Wrap failure. |

|

|

Built-in self test failure interrupt. |

|

|

Enables device internal message data buffer. |

|

|

Command block accessed interrupt (BC only). |

|

|

Enable bus channel A. |

|

|

Enable bus channel B. |

|

|

The offset in bytes to the Summit BC command block branch address pointer. |

|

|

The offset in bytes to the Summit BC command block 1553 command 1 word. |

|

|

The offset in bytes to the Summit BC command block 1553 command 2 word. |

|

|

The offset in bytes to the Summit BC command block control word. |

|

|

The offset in bytes to the Summit BC command block data pointer. |

|

|

The size in bytes of one Summit BC command block. |

|

|

The offset in bytes to the Summit BC command block 1553 status 1 word. |

|

|

The offset in bytes to the Summit BC command block 1553 status 2 word. |

|

|

The offset in bytes to the Summit BC command block time delay word. |

|

|

The number of nanoseconds the Summit built in self test takes to complete. 2 msec. |

|

|

The number of nanoseconds the Summit hardware reset line should be asserted. 1 usec. |

|

|

The number of nanoseconds the Summit software reset takes to complete. 12 usec. |

|

|

The offset in bytes to the Summit RT descriptor broadcast data pointer. |

|

|

The offset in bytes to the Summit RT descriptor control word. |

|

|

The offset in bytes to the Summit RT descriptor data pointer A. |

|

|

The offset in bytes to the Summit RT descriptor data pointer B. |

|

|

The size in bytes of one Summit RT descriptor entry. |

|

|

Device DMA failure interrupt. |

|

|

Allows node to accept dynamic bus control mode command. |

|

|

End of command list interrupt (BC only). |

|

|

Enable external timer clock. |

|

|

The device is executing normally. |

|

|

RT only - Broadcast command received. |

|

|

BC only - Command block accessed. |

|

|

BC only - End of command list. |

|

|

RT only - Illegal bus command word received. |

|

|

BC only - Illegal bus command word in command block. |

|

|

BC only - Illegal control opcode in command block. |

|

|

RT only - Index is 0 for a subaddress descriptor. |

|

|

MT only - Monitor block count is 0. |

|

|

Bus message error detected. |

|

|

BC only - Command retry failure. |

|

|

RT only - Subaddress accessed. |

|

|

Illegal bus command received interrupt (RT only). |

|

|

Illegal bus command attempted interrupt (BC only). |

|

|

Command block illegal opcode interrupt (BC only). |

|

|

Enables the interrupt log in shared memory. |

|

|

Index equal to 0 interrupt (RT only). |

|

|

Indicates the value of the device LOCK signal. |

|

|

Bus message error interrupt. |

|

|

Channel A or B. |

|

|

Illegal Command Received. |

|

|

Manchester Error. |

|

|

Message Error. |

|

|

Overrun Error. |

|

|

Parity Error. |

|

|

Remote Terminal to RT Xfer. |

|

|

Time-Out Error. |

|

|

Bits 15 - 11 Word Count Mask. |

|

|

Bit mask for the mode select. |

|

|

The mode select bits indicating bus controller function. |

|

|

The mode select bits indicating bus monitor function. |

|

|

The mode select bits indicating remote terminal function. |

|

|

Configuration-dependent message signaller. For boot configuration, a no-op. For application configuration, calls _msg_report().

|

|

|

Enables ping-pong of data buffers in shared memory. |

|

|

The device is ready for operation. |

|

|

Register 0C Offset: Summit BIT word register |

|

|

Register 04 Offset: Summit current command register |

|

|

Register 00 Offset: Summit control register |

|

|

Register 20 Offset: Illegal Receive 0 |

|

|

Register 22 Offset: Illegal Receive 1 |

|

|

Register 24 Offset: Illegal Transmit 0 |

|

|

Register 26 Offset: Illegal Transmit 1 |

|

|

Register 28 Offset: Illegal Broadcast Receive 0 |

|

|

Register 2A Offset: Illegal Broadcast Receive 1 |

|

|

Register 2C Offset: Illegal Broadcast Transmit 0 |

|

|

Register 2E Offset: Illegal Broadcast Transmit 1 |

|

|

Register 38 Offset: Illegal Mode Code Broadcast RCV 0 |

|

|

Register 3A Offset: Illegal Mode Code Broadcast RCV 1 |

|

|

Register 3C Offset: Illegal Mode Code Broadcase XMT 0 |

|

|

Register 3E Offset: Illegal Mode Code Broadcase XMT 1 |

|

|

Register 30 Offset: Illegal Mode Code Receive 0 |

|

|

Register 32 Offset: Illegal Mode Code Receive 1 |

|

|

Register 34 Offset: Illegal Mode Code Transmit 0 |

|

|

Register 36 Offset: Illegal Mode Code Transmit 1 |

|

|

Register 0A Offset: Summit interrupt log list pointer |

|

|

Register 06 Offset: Summit interrupt mask register |

|

|

Register 08 Offset: Summit interrupt pending register |

|

|

The number of times to retry writes to a Summit register if error are seen. |

|

|

Register 10 Offset: RT descriptor / BC command block pointer register |

|

|

Register 02 Offset: Summit status register |

|

|

Register 12 Offset: Summit 1553 status word register |

|

|

Register 0E Offset: Summit time tag register |

|

|

Write one 16-bit value to the Summit internal registers.

|

|

|

Ping-pong buffer indicator: 0 = buffer B, 1 = buffer A. |

|

|

Block accessed status bit. |

|

|

Broadcast message received. |

|

|

Interrupt when broadcast message received. |

|

|

Bit mask for message index value. |

|

|

Interrupt when index is 0. |

|

|

Interrupt when subaddress accessed. |

|

|

Enables Notice II operation concerning separation of broadcast data. |

|

|

Bit mask for the RT address value. |

|

|

Command block retry fail interrupt (BC only). |

|

|

The RT addres parity bit value. |

|

|

Start device built-in self test. |

|

|

Start device software reset. |

|

|

Indicates a critical device hardware error. |

|

|

Start normal bus processing. |

|

|

Subaddress accessed interrupt (RT only). |

|

|

Remote terminal busy flag. |

|

|

Remote terminal status immediate clear. |

|

|

Remote terminal instrumentation flag. |

|

|

Remote terminal service request flag. |

|

|

Remote termnial subsystem failure flag. |

|

|

Remote terminal terminal flag. |

|

|

Terminal address parity error interrupt (RT only). |

|

|

The device is busy processing a bus message. |

|

|

Indicates a parity error for the RT address value. |

|

|

Summit control register writable bit mask. |

|

|

Illegal XXX register writable bit mask. |

|

|

Summit interrupt log list pointer writable bit mask |

|

|

Summit interrupt mask register writable bit mask. |

|

|

RT descriptor / BC command block pointer register writable bit mask. |

|

|

Summit status register writable bit mask. |

|

|

Read one 16-bit value from the Summit internal registers or shared memory.

|

|

|

Write one 16-bit value to the Summit internal registers or shared memory.

|

|

|

Wrap fail interrupt. |

|

|

Allows automatic response to transmit last status word mode command. |

|

|

The typedef for structure _SUMT_Cmd_Blk. |

|

|

The typedef for _SUMT_Desc. |

|

|

The typedef for _SUMT_Log. |

|

|

The typedef for _SUMT_Regs. |

1.3.3

1.3.3