GLAST/LAT > DAQ and FSW > FSW > Doxygen Index > VXW / V7-0-3

Constituent: vxw_symbol Tag: rad750

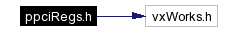

#include "vxWorks.h"

Include dependency graph for ppciRegs.h:

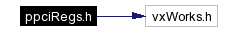

This graph shows which files directly or indirectly include this file:

Base Memory Map Definitions | |

| #define | PCI_IO_BASE_ADDR 0x80000000 |

| #define | PCI_CONFIG_ADDR_REG 0x80000CF8 |

| #define | PCI_CONFIG_DATA_REG 0x80000CFC |

| #define | PCI_CONFIG_BASE_ADDR 0x80800000 |

| #define | PCI_MEM_BASE_ADDR 0xC0000000 |

| #define | PPCI_BASE_ADDR 0xBF800000 |

| #define | ppciRegOffset(reg) ((ULONG)® - PPCI_BASE_ADDR) |

Memory Controller Definitions | |

| #define | ppciReserved0 (* (volatile ULONG *) 0xBF800000) |

| #define | ppciInitDataLow (* (volatile ULONG *) 0xBF800010) |

| #define | ppciInitDataHigh (* (volatile ULONG *) 0xBF800014) |

| #define | ppciInitStartAdr (* (volatile ULONG *) 0xBF800018) |

| #define | ppciInitEndingAdr (* (volatile ULONG *) 0xBF80001C) |

| #define | ppciMemBank0Adr (* (volatile ULONG *) 0xBF800020) |

| #define | ppciMemBank1Adr (* (volatile ULONG *) 0xBF800024) |

| #define | ppciMemBank2Adr (* (volatile ULONG *) 0xBF800028) |

| #define | ppciMemBank3Adr (* (volatile ULONG *) 0xBF80002C) |

| #define | ppciMemBank4Adr (* (volatile ULONG *) 0xBF800030) |

| #define | ppciMemBank5Adr (* (volatile ULONG *) 0xBF800034) |

| #define | ppciMemBank6Adr (* (volatile ULONG *) 0xBF800038) |

| #define | ppciMemBank7Adr (* (volatile ULONG *) 0xBF80003C) |

| #define | ppciMemType (* (volatile ULONG *) 0xBF800060) |

| #define | ppciMemAdrMode (* (volatile ULONG *) 0xBF800064) |

| #define | ppciMemBankEnable (* (volatile ULONG *) 0xBF800068) |

| #define | ppciMemBankWriteEnable (* (volatile ULONG *) 0xBF80006C) |

| #define | ppciCorrectionType (* (volatile ULONG *) 0xBF800070) |

| #define | ppciEccErrInject (* (volatile ULONG *) 0xBF800074) |

| #define | ppciMemScrubMode (* (volatile ULONG *) 0xBF800078) |

| #define | ppciMemScrubParms (* (volatile ULONG *) 0xBF80007C) |

| #define | ppciMemBank0Sparing (* (volatile ULONG *) 0xBF800080) |

| #define | ppciMemBank1Sparing (* (volatile ULONG *) 0xBF800084) |

| #define | ppciMemBank2Sparing (* (volatile ULONG *) 0xBF800088) |

| #define | ppciMemBank3Sparing (* (volatile ULONG *) 0xBF80008C) |

| #define | ppciMemBank4Sparing (* (volatile ULONG *) 0xBF800090) |

| #define | ppciMemBank5Sparing (* (volatile ULONG *) 0xBF800094) |

| #define | ppciMemBank6Sparing (* (volatile ULONG *) 0xBF800098) |

| #define | ppciMemBank7Sparing (* (volatile ULONG *) 0xBF80009C) |

| #define | ppciMemStatus (* (volatile ULONG *) 0xBF8000C0) |

| #define | ppciMemIntEnable (* (volatile ULONG *) 0xBF8000C4) |

| #define | ppciMemErrLog1 (* (volatile ULONG *) 0xBF8000C8) |

| #define | ppciMemErrLog2 (* (volatile ULONG *) 0xBF8000CC) |

| #define | ppciMemErrCounter (* (volatile ULONG *) 0xBF8000D0) |

| #define | ppciMemErrLogRC1 (* (volatile ULONG *) 0xBF8000D8) |

| #define | ppciMemErrLogRC2 (* (volatile ULONG *) 0xBF8000DC) |

| #define | ppciSdramConf (* (volatile ULONG *) 0xBF8000E0) |

| #define | ppciSdramTimingParms1 (* (volatile ULONG *) 0xBF8000E8) |

| #define | ppciSdramTimingParms2 (* (volatile ULONG *) 0xBF8000EC) |

| #define | ppciRomTimingParms (* (volatile ULONG *) 0xBF8000F0) |

| #define | ppciSramTimingParms (* (volatile ULONG *) 0xBF8000F4) |

| #define | MAX_NUM_MEM_BANKS 8 |

| #define | MEM_INIT_BOUNDARY_MASK 0x0000001F |

| #define | MEM_INIT_IN_PROGRESS 0x00000001 |

| #define | MEM_BANK_REG(base_addr, num_bytes) |

| #define | GET_MEM_BANK_BASE(reg_value) ((reg_value) & 0xFFFF0000) |

| #define | GET_MEM_BANK_LIMIT(reg_value) ((((reg_value) & 0xFFFF) + 1) << 16) |

| #define | BANK0_SCRUB_MODE_MASK 0x00000003 |

| #define | SCRUB_MODE_SHIFT 2 |

| #define | MEM_BANK_TYPE(bank, type) ((type) << ((bank) * 2)) |

| #define | GET_MEM_BANK_TYPE(bank, reg_value) (((reg_value) >> ((bank) * 2)) & 0x00000003) |

| #define | MEM_ADDRESS_PARITY_CORRECTION(bank) (1 << (16 + (bank))) |

| #define | MEM_CORRECTION_TYPE(bank, type) ((type) << ((bank) * 2)) |

| #define | ERR_LOG_FIFO_DEPTH 4 |

| #define | ERR_LOG_ENTRY_VALID 0x80000000 |

| #define | ERR_LOG_WRITE_ERROR 0x40000000 |

| #define | ERR_LOG_SOURCE_INTERNAL 0x20000000 |

| #define | ERR_LOG_ERROR_TYPE_MASK 0x1F000000 |

| #define | ERR_LOG_ERROR_TYPE_SHIFT 24 |

| #define | NUM_MEM_INT_LVLS 32 |

| #define | ERR_LOG_ERROR_LOC_MASK 0x001F0000 |

| #define | ERR_LOG_ERROR_LOC_SHIFT 16 |

| #define | ERR_LOG_ERROR_SYN_MASK 0x0000FFFF |

| #define | SRAM_TIMING_BURST_ENABLE_BIT 16 |

| #define | SRAM_TIMING_WAIT_CYCLE_MASK 0xF |

| #define | SRAM_TIMING_NEXT_WAIT_READ_SHIFT 12 |

| #define | SRAM_TIMING_NEXT_WAIT_WRITE_SHIFT 8 |

| #define | SRAM_TIMING_FIRST_WAIT_READ_SHIFT 4 |

| #define | SRAM_TIMING_FIRST_WAIT_WRITE_SHIFT 0 |

| #define | SDRAM_MODE_REG_SET_VAL_MASK 0x3fff0000 |

| #define | SDRAM_MODE_REG_SET_VAL_SHIFT 16 |

| #define | SDRAM_CTRL_ENABLE_BIT 15 |

| #define | SDRAM_SELF_REFRESH_BIT 14 |

| #define | SDRAM_STP_CLK_IN_SELF_REFRESH_BIT 13 |

| #define | SDRAM_AUTO_PRECHARGE_ENABLE_BIT 12 |

| #define | SDRAM_ADDR_SETUP_ENABLE_BIT 11 |

| #define | SDRAM_TIMING1_MAX_BANK_ACTIVE_MASK 0x000000FF |

| #define | SDRAM_TIMING1_MAX_BANK_ACTIVE_SHIFT 0 |

| typedef enum memScrubMode | memScrubMode_t |

| typedef enum memBankType | memBankType_t |

| typedef enum memCorrectionType | memCorrectionType_t |

| typedef enum memErrorType | memErrorType_t |

| enum | memScrubMode { SCRUB_DISABLED = 0, SCRUB_PASSIVE = 1, SCRUB_ACTIVE = 2, SCRUB_ACTIVE_ALWAYS = 3 } |

| enum | memBankType { MEM_TYPE_ROM = 0, MEM_TYPE_SRAM = 1, MEM_TYPE_SDRAM = 2 } |

| enum | memCorrectionType { MEM_ODD_PARITY = 0, MEM_SECDED = 1, MEM_NIBBLE_CORRECT = 2, MEM_NO_CORRECTION = 3 } |

| enum | memErrorType { MEM_ERR_CORR_SINGLE_BIT = 0x03, MEM_ERR_CORR_MULTI_BIT = 0x04, MEM_ERR_UNCORR_DATA_ERR = 0x05, MEM_ERR_UNCORR_ADDR_ERR = 0x06, MEM_ERR_ADDR_OUT_OF_BNDS = 0x07, MEM_ERR_ROM_WRT_ATTEMPT = 0x08, MEM_ERR_MCI_INV_CMD = 0x0A, MEM_ERR_MCI_INV_ADDR = 0x0B, MEM_ERR_MCI_WRT_BEPE = 0x0C, MEM_ERR_MCI_WRT_DPE = 0x0D, MEM_ERR_MCI_APE = 0x0E, MEM_ERR_MRI_INV_REQ = 0x0F, MEM_ERR_MRI_WRT_BEPE = 0x10, MEM_ERR_MRI_WRT_DPE = 0x11, MEM_ERR_MRI_APE = 0x12 } |

P60X Interface Definitions | |

| #define | ppciReserved1 (* (volatile ULONG *) 0xBF810000) |

| #define | ppciBusErrStatus (* (volatile ULONG *) 0xBF810008) |

| #define | ppciBusErrAdr (* (volatile ULONG *) 0xBF81000C) |

| #define | ppciErrStatus (* (volatile ULONG *) 0xBF810010) |

| #define | ppciErrStatusMask (* (volatile ULONG *) 0xBF810014) |

| #define | ppciErrInject60x (* (volatile ULONG *) 0xBF810018) |

| #define | OCB_MCP 0x00000010 |

| #define | MCP_60X 0x00000008 |

| #define | OCB_IF_ERR 0x00000004 |

| #define | ADDR_OUT_OF_RANGE 0x00000002 |

| #define | MEM_CTRL_IF_ERR 0x00000001 |

| #define | NUM_P60X_INT_LVLS 3 |

UART Definitions | |

| #define | ppciRecvBuffer (* (volatile UCHAR *) 0xBF820000) |

| #define | ppciTransHolding (* (volatile UCHAR *) 0xBF820000) |

| #define | ppciUartIntEnable (* (volatile UCHAR *) 0xBF820001) |

| #define | ppciDivLow (* (volatile UCHAR *) 0xBF820000) |

| #define | ppciDivHigh (* (volatile UCHAR *) 0xBF820001) |

| #define | ppciIntId (* (volatile UCHAR *) 0xBF820002) |

| #define | ppciFifoCtl (* (volatile UCHAR *) 0xBF820002) |

| #define | ppciLineCtl (* (volatile UCHAR *) 0xBF820003) |

| #define | ppciModemCtl (* (volatile UCHAR *) 0xBF820004) |

| #define | ppciLineStatus (* (volatile UCHAR *) 0xBF820005) |

| #define | ppciModemStatus (* (volatile UCHAR *) 0xBF820006) |

| #define | ppciScratchPad (* (volatile UCHAR *) 0xBF820007) |

| #define | ppciErrorStatus (* (volatile UCHAR *) 0xBF820008) |

JTAG Definitions | |

| #define | ppciJtagCSRA (* (volatile ULONG *) 0xBF830000) |

| #define | ppciJtagBitCntA (* (volatile ULONG *) 0xBF830004) |

| #define | ppciJtagTDIA (* (volatile ULONG *) 0xBF830008) |

| #define | ppciJtagTDOA (* (volatile ULONG *) 0xBF83000C) |

| #define | ppciJtagTCLKDivA (* (volatile ULONG *) 0xBF830010) |

| #define | ppciJtagFuncIDA (* (volatile ULONG *) 0xBF830014) |

| #define | ppciReservedA0 (* (volatile ULONG *) 0xBF830018) |

| #define | ppciReservedA1 (* (volatile ULONG *) 0xBF83001C) |

| #define | ppciJtagCsrr (* (volatile ULONG *) 0xBF840000) |

| #define | ppciJtagBitCntB (* (volatile ULONG *) 0xBF840004) |

| #define | ppciJtagTdib (* (volatile ULONG *) 0xBF840008) |

| #define | ppciJtagTdob (* (volatile ULONG *) 0xBF84000C) |

| #define | ppciJtagTclkDivB (* (volatile ULONG *) 0xBF840010) |

| #define | ppciJtagFuncIDB (* (volatile ULONG *) 0xBF840014) |

| #define | ppciReservedB0 (* (volatile ULONG *) 0xBF840018) |

| #define | ppciReservedB1 (* (volatile ULONG *) 0xBF84001C) |

EMC Controller Definitions | |

| #define | ppciCondStatus (* (volatile ULONG *) 0xBF85002C) |

| #define | ppciVecIntAdr (* (volatile ULONG *) 0xBF850030) |

| #define | ppciVecCtl (* (volatile ULONG *) 0xBF850034) |

| #define | ppciVectAnchor (* (volatile ULONG *) 0xBF850038) |

| #define | ppciEmcWatchdogTimer (* (volatile ULONG *) 0xBF85003C) |

| #define | ppciProgramCounter (* (volatile ULONG *) 0xBF850040) |

| #define | ppciBrkptAdr (* (volatile ULONG *) 0xBF850044) |

| #define | ppciDbgCmdStatus (* (volatile ULONG *) 0xBF850048) |

| #define | ppciEmcErrIntStatus (* (volatile ULONG *) 0xBF85004C) |

| #define | VECTOR_7_PENDING 0x80000000 |

| #define | VECTOR_6_PENDING 0x40000000 |

| #define | VECTOR_5_PENDING 0x20000000 |

| #define | VECTOR_4_PENDING 0x10000000 |

| #define | VECTOR_3_PENDING 0x08000000 |

| #define | VECTOR_2_PENDING 0x04000000 |

| #define | VECTOR_1_PENDING 0x02000000 |

| #define | VECTOR_0_PENDING 0x01000000 |

| #define | VECTOR_5_ENABLE 0x00200000 |

| #define | VECTOR_4_ENABLE 0x00100000 |

| #define | VECTOR_3_ENABLE 0x00080000 |

| #define | VECTOR_2_ENABLE 0x00040000 |

| #define | VECTOR_1_ENABLE 0x00020000 |

| #define | VECTOR_0_ENABLE 0x00010000 |

| #define | VECTOR_7_STOP 0x00008000 |

| #define | VECTOR_6_STOP 0x00004000 |

| #define | VECTOR_5_STOP 0x00002000 |

| #define | VECTOR_4_STOP 0x00001000 |

| #define | VECTOR_3_STOP 0x00000800 |

| #define | VECTOR_2_STOP 0x00000400 |

| #define | VECTOR_1_STOP 0x00000200 |

| #define | VECTOR_0_STOP 0x00000100 |

| #define | STOP_ON_VECTOR_ENABLE 0x00000080 |

Clock Control Definitions | |

| #define | ppciClkCtl (* (volatile ULONG *) 0xBF860000) |

| #define | ppciPllSetup (* (volatile ULONG *) 0xBF860004) |

| #define | ppciPllConfiguration (* (volatile ULONG *) 0xBF860008) |

| #define | ppciPmControl (* (volatile ULONG *) 0xBF86000C) |

| #define | ppciCtErrIntStatus (* (volatile ULONG *) 0xBF860010) |

| #define | ppciCtRevID (* (volatile ULONG *) 0xBF860014) |

| #define | ppciZeroPad0 (* (volatile ULONG *) 0xBF860018) |

| #define | ppciZeroPad1 (* (volatile ULONG *) 0xBF86001C) |

| #define | ppciBistMISRLow (* (volatile ULONG *) 0xBF860020) |

| #define | ppciBistMISRHigh (* (volatile ULONG *) 0xBF860024) |

| #define | ppciBistCtl (* (volatile ULONG *) 0xBF860028) |

| #define | ppciBistStatus (* (volatile ULONG *) 0xBF86002C) |

| #define | ppciBistID (* (volatile ULONG *) 0xBF860030) |

| #define | ppciZeroPad2 (* (volatile ULONG *) 0xBF860034) |

| #define | ppciZeroPad3 (* (volatile ULONG *) 0xBF860038) |

| #define | ppciZeroPad4 (* (volatile ULONG *) 0xBF86003C) |

| #define | ppciBistSoftReset (* (volatile ULONG *) 0xBF860040) |

| #define | ppciBistStopClks (* (volatile ULONG *) 0xBF860044) |

| #define | ppciBistStartClks (* (volatile ULONG *) 0xBF860048) |

| #define | ppciBistSingleCycle (* (volatile ULONG *) 0xBF86004C) |

| #define | ppciBistStartLBist (* (volatile ULONG *) 0xBF860050) |

| #define | ppciBistStartABist (* (volatile ULONG *) 0xBF860054) |

| #define | ppciBistStartLabScan (* (volatile ULONG *) 0xBF860058) |

| #define | ppciBistCycleCnt (* (volatile ULONG *) 0xBF86005C) |

| #define | PCI_CLK_DIV_MASK 0x00000030 |

| #define | PCI_CLK_DIV_SHIFT 4 |

| #define | PCI_CLK_DIV_LOG2_MIN_DIV 0 |

| #define | RTC_CLK_DIV_MASK 0x0000000C |

| #define | RTC_CLK_DIV_SHIFT 2 |

| #define | RTC_CLK_DIV_LOG2_MIN_DIV 2 |

| #define | SYS_CLK_DIV_MASK 0x00000003 |

| #define | SYS_CLK_DIV_SHIFT 0 |

| #define | SYS_CLK_DIV_LOG2_MIN_DIV 0 |

| #define | CLK_REG_TO_MULT(Reg_Val, Clock) |

| #define | PPCI_PWR_MGMT_ENABLE 0x80000000 |

| #define | PPCI_PWR_MGMT_SEL_MASK 0x70000000 |

| #define | PPCI_SLEEP 0x40000000 |

| #define | PPCI_NAP 0x20000000 |

| #define | PPCI_DOZE 0x10000000 |

| #define | PPCI_PLL_ENABLE 0x00000010 |

| #define | PPCI_PLL_CFG_MASK 0x0000000F |

| #define | CAT_WRITE_ACC_ERR_BIT 31 |

| #define | CAT_ADDR_PHASE_PAR_ERR_BIT 30 |

| #define | CAT_WRITE_DATA_PAR_ERR_BIT 29 |

| #define | CAT_ADDR_OUT_OF_RNG_BIT 28 |

| #define | PPCI_BIST_STATUS_RESET_POR (0x00000001) |

| #define | PPCI_BIST_STATUS_RESET_INTERN (0x00000002) |

| #define | PPCI_BIST_STATUS_RESET_OCB (0x00000004) |

| #define | PPCI_BIST_STATUS_RESET_JTAG (0x00000008) |

| #define | PPCI_BIST_STATUS_RESET_MASK (0x0000000F) |

| typedef enum ppciPllMult | ppciPllMult_t |

| enum | ppciPllMult { PLL_BYPASS = 0xC, PLL_2x = 0x2, PLL_2_5x = 0x6, PLL_3x = 0x1, PLL_3_5x = 0x7, PLL_4x = 0x5, PLL_4_5x = 0xE, PLL_5x = 0xD, PLL_5_5x = 0x9, PLL_6x = 0xB, PLL_6_5x = 0xA, PLL_7x = 0x4, PLL_7_5x = 0x8, PLL_8x = 0x3 } |

PCI Interface Definitions | |

| #define | ppciPciVendorID (* (volatile USHORT*) 0xBF870000) |

| #define | ppciPciDeviceID (* (volatile USHORT*) 0xBF870002) |

| #define | ppciPciCommand (* (volatile USHORT*) 0xBF870004) |

| #define | ppciPciStatus (* (volatile USHORT*) 0xBF870006) |

| #define | ppciPciRevID (* (volatile UCHAR *) 0xBF870008) |

| #define | ppciClassCodeProg (* (volatile UCHAR *) 0xBF870009) |

| #define | ppciClassCodeSubBase (* (volatile USHORT*) 0xBF87000A) |

| #define | ppciCachelineSize (* (volatile UCHAR *) 0xBF87000C) |

| #define | ppciLatencyTimer (* (volatile UCHAR *) 0xBF87000D) |

| #define | ppciHeaderType (* (volatile UCHAR *) 0xBF87000E) |

| #define | ppciBaseAdr1 (* (volatile ULONG *) 0xBF870010) |

| #define | ppciBaseAdr2 (* (volatile ULONG *) 0xBF870018) |

| #define | ppciSubsystemVendorID (* (volatile USHORT*) 0xBF87002C) |

| #define | ppciSubsystemID (* (volatile USHORT*) 0xBF87002E) |

| #define | ppciIntLine (* (volatile UCHAR *) 0xBF87003C) |

| #define | ppciIntPin (* (volatile UCHAR *) 0xBF87003D) |

| #define | ppciMinGnt (* (volatile UCHAR *) 0xBF87003E) |

| #define | ppciMaxLat (* (volatile UCHAR *) 0xBF87003F) |

| #define | ppciPciStatus2 (* (volatile ULONG *) 0xBF870050) |

| #define | ppciPciStatus2Mask (* (volatile ULONG *) 0xBF870054) |

| #define | ppciBar1SizeAdjust (* (volatile ULONG *) 0xBF870058) |

| #define | ppciPciConfig (* (volatile ULONG *) 0xBF87005C) |

| #define | ppciArbPriority (* (volatile USHORT*) 0xBF870060) |

| #define | ppciPciErrChecking (* (volatile USHORT*) 0xBF870062) |

| #define | ppciPciErrInject (* (volatile UCHAR *) 0xBF870064) |

| #define | ppciPciBusReset (* (volatile UCHAR *) 0xBF870065) |

| #define | ppciRevID (* (volatile USHORT*) 0xBF870066) |

| #define | ppciO2pioPag0 (* (volatile USHORT*) 0xBF870080) |

| #define | ppciO2pioPag1 (* (volatile USHORT*) 0xBF870082) |

| #define | ppciO2pioPag2 (* (volatile USHORT*) 0xBF870084) |

| #define | ppciO2pioPag3 (* (volatile USHORT*) 0xBF870086) |

| #define | ppciO2pioPag4 (* (volatile USHORT*) 0xBF870088) |

| #define | ppciO2pioPag5 (* (volatile USHORT*) 0xBF87008A) |

| #define | ppciO2pioPag6 (* (volatile USHORT*) 0xBF87008C) |

| #define | ppciO2pioPag7 (* (volatile USHORT*) 0xBF87008E) |

| #define | ppciO2PmemPag0 (* (volatile USHORT*) 0xBF870090) |

| #define | ppciO2PmemPag1 (* (volatile USHORT*) 0xBF870092) |

| #define | ppciO2PmemPag2 (* (volatile USHORT*) 0xBF870094) |

| #define | ppciO2PmemPag3 (* (volatile USHORT*) 0xBF870096) |

| #define | ppciO2PmemPag4 (* (volatile USHORT*) 0xBF870098) |

| #define | ppciO2PmemPag5 (* (volatile USHORT*) 0xBF87009A) |

| #define | ppciO2PmemPag6 (* (volatile USHORT*) 0xBF87009C) |

| #define | ppciO2PmemPag7 (* (volatile USHORT*) 0xBF87009E) |

| #define | ppciUserDefinedB (* (volatile ULONG *) 0xBF8700A8) |

| #define | ppciUserDefinedC (* (volatile ULONG *) 0xBF8700AC) |

| #define | ppciUserDefinedA (* (volatile ULONG *) 0xBF8700C0) |

| #define | ppciPciBusErrStatus (* (volatile USHORT*) 0xBF8700C6) |

| #define | ppciPciErrAdr (* (volatile ULONG *) 0xBF8700C8) |

| #define | PPCI_MEM_BAR_NUM 0 |

| #define | PPCI_REGS_BAR_NUM 2 |

| #define | PPCI_REGS_SPACE_SIZE 0x100000 |

| #define | BAR2_PREFETCH 0x08000000 |

| #define | BAR2_SPEC_READ 0x04000000 |

| #define | BAR1_PREFETCH 0x02000000 |

| #define | BAR1_SPEC_READ 0x01000000 |

| #define | FORCE_IMMED_DISC 0x00400000 |

| #define | FORCE_IMMED_DELAYED_TRANS 0x00200000 |

| #define | BAR2_WRITE_DIS 0x00100000 |

| #define | DISCARD_TIMER_DIS 0x00080000 |

| #define | TGT_SUB_LAT_DIS 0x00040000 |

| #define | TGT_INIT_LAT_DIS 0x00020000 |

| #define | HOST_BUS_TGT_LAT 0x00010000 |

| #define | MEM_COMB_DIS 0x00000200 |

| #define | IO_COMB_DIS 0x00000100 |

| #define | MASTER_ABORT_IGN 0x00000080 |

| #define | MEM_READ_CTRL_MASK 0x00000060 |

| #define | MEM_READ_LINE 0x00000040 |

| #define | MEM_READ_MULT 0x00000060 |

| #define | DIS_OSR_ORDERING 0x00000010 |

| #define | LAT_TIMER_DIS 0x00000004 |

| #define | IO_PAGE_MODE 0x00000002 |

| #define | MEM_PAGE_MODE 0x00000001 |

| #define | DETECTED_PARITY_ERR 0x80000000 |

| #define | SIGNALLED_SYSTEM_ERR 0x40000000 |

| #define | RECEIVED_MASTER_ABORT 0x20000000 |

| #define | RECEIVED_TARGET_ABORT 0x10000000 |

| #define | SIGNALED_TARGET_ABORT 0x08000000 |

| #define | DEVSEL_TIMING_MASK 0x06000000 |

| #define | MASTER_DATA_PARITY_ERR 0x01000000 |

| #define | PCI_OCB_MSTR_READ_ERR 0x00800000 |

| #define | PCI_OCB_MSTR_DATA_PAR_ERR 0x00400000 |

| #define | PCI_OCB_WRT_BUFF_PAR_ERR 0x00200000 |

| #define | PCI_OCB_SLV_BE_PAR_ERR 0x00100000 |

| #define | PCI_OCB_SLV_DATA_PAR_ERR 0x00080000 |

| #define | PCI_INVALID_OCB_ACC 0x00040000 |

| #define | PCI_INVALID_OCB_ADDR 0x00020000 |

| #define | PCI_OCB_ADDR_PAR_ERR 0x00010000 |

| #define | PCI_INTERNAL_ERR 0x00008000 |

| #define | PCI_RESET_DETECTED 0x00004000 |

| #define | PCI_PROTOCOL_ERR 0x00002000 |

| #define | PCI_SERR_DETECTED 0x00001000 |

| #define | PCI_BUS_ADDR_PAR_ERR 0x00000800 |

| #define | PCI_ARBITER_TIMEOUT 0x00000400 |

| #define | PCI_DATA_PHASE_TIMEOUT 0x00000200 |

| #define | PCI_ARB_LAT_TIMEOUT 0x00000100 |

| #define | PCI_INIT_PERR_RECEIVED 0x00000040 |

| #define | PCI_INIT_DATA_PAR_ERR 0x00000020 |

| #define | PCI_INIT_READY_PAR_ERR 0x00000010 |

| #define | PCI_MEM_SPACE_OVERLAP 0x00000008 |

| #define | PCI_TARGET_PERR_RECEIVE 0x00000004 |

| #define | PCI_TARGET_DATA_PAR_ERR 0x00000002 |

| #define | PCI_TARGET_READY_PAR_ERR 0x00000001 |

| #define | NUM_PCI_INT_LVLS 32 |

| #define | PPCI_PROT_CHK_ENABLE_BIT 10 |

| #define | PPCI_READY_PARITY_ENABLE_BIT 9 |

| #define | PPCI_DATA_PHASE_TO_SHIFT 4 |

| #define | PPCI_DATA_PHASE_TO_ENABLE_BIT 3 |

| #define | PPCI_ARB_LAT_TO_SHIFT 1 |

| #define | PPCI_ARB_LAT_TO_ENABLE_BIT 0 |

| #define | USERA_60X_ERR_ENABLE 0x00000001 |

| #define | USERB_WAIT_STATE_MASK 0x00C00000 |

| #define | USERB_WAIT_STATE_SHIFT 22 |

| #define | USERB_MACH_CHK_ENABLE 0x00000800 |

| #define | USERB_LITTLE_ENDIAN 0x00000020 |

| #define | PPCI_PCI_BUS_RESET_CEN_RSRS (0x10) |

| #define | PPCI_PCI_BUS_RESET_ACTIVE (0x01) |

| typedef enum ppci_data_phase_timeout_type | PPCI_DATA_PHASE_TIMEOUT_TYPE |

| typedef enum ppci_arb_lat_timeout_type | PPCI_ARB_LAT_TIMEOUT_TYPE |

| enum | ppci_data_phase_timeout_type { PPCI_DATA_PHASE_256_CYCLE_TO, PPCI_DATA_PHASE_512_CYCLE_TO, PPCI_DATA_PHASE_1024_CYCLE_TO, PPCI_DATA_PHASE_2048_CYCLE_TO } |

| enum | ppci_arb_lat_timeout_type { PPCI_ARB_LAT_256_CYCLE_TO, PPCI_ARB_LAT_512_CYCLE_TO, PPCI_ARB_LAT_1024_CYCLE_TO, PPCI_ARB_LAT_2048_CYCLE_TO } |

Interrupt Controller Definitions | |

| #define | ppciIntCollection (* (volatile ULONG *) 0xBF880000) |

| #define | ppciIntEnableReg (* (volatile ULONG *) 0xBF880004) |

| #define | NUM_PPCI_INT_LVLS 32 |

| #define | NUM_MISC_INT_LVLS 32 |

PID Interface Definitions | |

| #define | ppciPidOutputEnable (* (volatile ULONG *) 0xBF880008) |

| #define | ppciPidOutputSelect (* (volatile ULONG *) 0xBF88000C) |

| #define | ppciPidOutput (* (volatile ULONG *) 0xBF880010) |

| #define | ppciPidInputEnable (* (volatile ULONG *) 0xBF880014) |

| #define | ppciPidInputSelect (* (volatile ULONG *) 0xBF880018) |

| #define | ppciPidIntEnable (* (volatile ULONG *) 0xBF88001C) |

| #define | ppciPidVecEnable (* (volatile ULONG *) 0xBF880020) |

| #define | ppciPidInput (* (volatile ULONG *) 0xBF880024) |

| #define | NUM_PIDS 32 |

| #define | PTIM1_OUT_PID 0 |

| #define | PTIM2_OUT_PID 1 |

| #define | PTIM3_OUT_PID 2 |

| #define | WDT_EXPIRED_PID 3 |

| #define | WDT_HEARTBEAT_PID 4 |

| #define | PTIM1_EXT_CLK_PID 5 |

| #define | PTIM1_SNAP_TRIG_PID 6 |

| #define | PTIM1_EXT_CLR_PID 7 |

| #define | PTIM2_EXT_CLK_PID 8 |

| #define | PTIM2_SNAP_TRIG_PID 9 |

| #define | PTIM2_EXT_CLR_PID 10 |

| #define | PTIM3_EXT_CLK_PID 11 |

| #define | PTIM3_SNAP_TRIG_PID 12 |

| #define | PTIM3_EXT_CLR_PID 13 |

| typedef enum ppciPidInSel | ppciPidInSel_t |

| typedef enum ppciPidOutSel | ppciPidOutSel_t |

| enum | ppciPidInSel { PID_IN_ACTIVE_LOW = 0, PID_IN_NEG_EDGE = 1 } |

| enum | ppciPidOutSel { PID_OUT_REG = 0, PID_OUT_TIMER = 1 } |

CPU Discretes Inteface Definitions | |

| #define | ppciCpuDiscretes (* (volatile ULONG *) 0xBF880028) |

| #define | ppciMcpCollection (* (volatile ULONG *) 0xBF88002C) |

| #define | ppciMcpEnable (* (volatile ULONG *) 0xBF880030) |

| #define | MCP_INTERNAL_MCP_MASK 0x00000006 |

| #define | MCP_INTERNAL_MCP_SHIFT 1 |

| #define | MCP_NMI_ENABLE 0x00000001 |

Programmable Timer Definitions | |

| #define | ppciPtim1Conf (* (volatile ULONG *) 0xBF880034) |

| #define | ppciPtim1Timer (* (volatile ULONG *) 0xBF880038) |

| #define | ppciPtim1Reload (* (volatile ULONG *) 0xBF88003C) |

| #define | ppciPtim2Conf (* (volatile ULONG *) 0xBF880040) |

| #define | ppciPtim2Timer (* (volatile ULONG *) 0xBF880044) |

| #define | ppciPtim2Reload (* (volatile ULONG *) 0xBF880048) |

| #define | ppciPtim3Conf (* (volatile ULONG *) 0xBF88004C) |

| #define | ppciPtim3Timer (* (volatile ULONG *) 0xBF880050) |

| #define | ppciPtim3Reload (* (volatile ULONG *) 0xBF880054) |

| #define | ppciWatchdogTimer (* (volatile ULONG *) 0xBF880058) |

| #define | PTIM_ENABLE_BIT 31 |

| #define | PTIM_CNT_DIR_BIT 30 |

| #define | PTIM_SOURCE_BIT 29 |

| #define | PTIM_FREQ_SEL_BIT 28 |

| #define | PTIM_TERM_EVT_BIT 27 |

| #define | PTIM_TERM_SIG_BIT 26 |

| #define | PTIM_PULSE_TOG_BIT 25 |

| #define | PTIM_SNAP_BIT 24 |

| #define | PTIM_EXT_CLR_BIT 23 |

| #define | PTIM_ENABLE (1 << PTIM_ENABLE_BIT) |

Multiprocessor Interface Definitions | |

| #define | ppciSemAll (* (volatile ULONG *) 0xBF88005C) |

| #define | ppciSem0 (* (volatile UCHAR *) 0xBF880060) |

| #define | ppciSem1 (* (volatile UCHAR *) 0xBF880061) |

| #define | ppciSem2 (* (volatile UCHAR *) 0xBF880062) |

| #define | ppciSem3 (* (volatile UCHAR *) 0xBF880063) |

| #define | ppciSem4 (* (volatile UCHAR *) 0xBF880064) |

| #define | ppciSem5 (* (volatile UCHAR *) 0xBF880065) |

| #define | ppciSem6 (* (volatile UCHAR *) 0xBF880066) |

| #define | ppciSem7 (* (volatile UCHAR *) 0xBF880067) |

| #define | ppciSem8 (* (volatile UCHAR *) 0xBF880068) |

| #define | ppciSem9 (* (volatile UCHAR *) 0xBF880069) |

| #define | ppciSemA (* (volatile UCHAR *) 0xBF88006A) |

| #define | ppciSemB (* (volatile UCHAR *) 0xBF88006B) |

| #define | ppciSemC (* (volatile UCHAR *) 0xBF88006C) |

| #define | ppciSemD (* (volatile UCHAR *) 0xBF88006D) |

| #define | ppciSemE (* (volatile UCHAR *) 0xBF88006E) |

| #define | ppciSemF (* (volatile UCHAR *) 0xBF88006F) |

| #define | ppciSem10 (* (volatile UCHAR *) 0xBF880070) |

| #define | ppciSem11 (* (volatile UCHAR *) 0xBF880071) |

| #define | ppciSem12 (* (volatile UCHAR *) 0xBF880072) |

| #define | ppciSem13 (* (volatile UCHAR *) 0xBF880073) |

| #define | ppciSem14 (* (volatile UCHAR *) 0xBF880074) |

| #define | ppciSem15 (* (volatile UCHAR *) 0xBF880075) |

| #define | ppciSem16 (* (volatile UCHAR *) 0xBF880076) |

| #define | ppciSem17 (* (volatile UCHAR *) 0xBF880077) |

| #define | ppciSem18 (* (volatile UCHAR *) 0xBF880078) |

| #define | ppciSem19 (* (volatile UCHAR *) 0xBF880079) |

| #define | ppciSem1A (* (volatile UCHAR *) 0xBF88007A) |

| #define | ppciSem1B (* (volatile UCHAR *) 0xBF88007B) |

| #define | ppciSem1C (* (volatile UCHAR *) 0xBF88007C) |

| #define | ppciSem1D (* (volatile UCHAR *) 0xBF88007D) |

| #define | ppciSem1E (* (volatile UCHAR *) 0xBF88007E) |

| #define | ppciSem1F (* (volatile UCHAR *) 0xBF88007F) |

| #define | ppciMultiprocSigSet (* (volatile ULONG *) 0xBF880080) |

| #define | ppciMultiprocSigClear (* (volatile ULONG *) 0xBF880084) |

| #define | ppciSignalIntEnable (* (volatile ULONG *) 0xBF880088) |

| #define | ppciVecIntStatus (* (volatile ULONG *) 0xBF88008C) |

| #define | ppciVecIntEnable (* (volatile ULONG *) 0xBF880090) |

| #define | ppciMiscIntStatus (* (volatile ULONG *) 0xBF880094) |

| #define | ppciMiscIntEnable (* (volatile ULONG *) 0xBF880098) |

| #define | NUM_MP_SIGNALS 32 |

| #define | NUM_MP_SEMS 32 |

| typedef enum mpSemVal | mpSemVal_t |

| enum | mpSemVal { MP_SEM_FREE = 0, MP_SEM_TAKEN = 1 } |

Description: This header file contains constants for the RAD750 PowerPCI chip registers. All cores are included.

Change History: 991105 mjf created

Copyright 1999 Lockheed Martin Space Electronics and Communications

|

|

Value: (1 << (((Reg_Val & Clock##_CLK_DIV_MASK) >> Clock##_CLK_DIV_SHIFT) + \

Clock##_CLK_DIV_LOG2_MIN_DIV))

|

|

|

The number of entries in the memory controller log. |

|

|

Macro returns memory bank base address from register value. |

|

|

Macro returns memory bank upper address from register value. |

|

|

Extracts bank type from memory controller register. |

|

|

The number of memory banks supported in hardware. |

|

|

Macro returns address parity bit mask for a bank. |

|

|

Value: (((base_addr) & 0xFFFF0000) | \ ((((base_addr) + (num_bytes) + 0xFFFF) >> 16) - 1)) |

|

|

Returns bank type bit mask for a bank. |

|

|

Macro returns address EDAC type bit mask for a bank. |

|

|

The number of memory controller interrupt levels. |

|

|

The number of PPCI miscellaneous interrupt levels. |

|

|

The number of multiprocessor interrupt semaphores. |

|

|

The number of multiprocessor interrupt signals. |

|

|

The number of P60X error interrupt levels |

|

|

The number of PCI interface error interrupt levels. |

|

|

The number of PID's available. |

|

|

The number of PPCI master interrupt levels. |

|

|

The CPU address of the PCI config address port register. |

|

|

The base address of PCI config space. |

|

|

The CPU address of the PCI config data port register. |

|

|

The CPU address of PCI I/O space. |

|

|

The CPU address of PCI Mem space. |

|

|

The CPU address of the PPCI chip internal registers. |

|

|

The size in bytes of the PPCI register space. |

|

|

Macro to caculate PPCI register relative address offset. |

|

|

The typedef for memBankType_t. |

|

|

The typedef for memCorrectionType. |

|

|

The typedef for memErrorType. |

|

|

The typedef for memScrubMode. |

|

|

The typedef for mpSemVal. |

|

|

The typedef for ppci_arb_lat_timeout_type. |

|

|

The typedef for ppci_data_phase_timeout_type. |

|

|

The typedef for ppciPidInSel. |

|

|

The typedef for ppciPidOutSel. |

|

|

The typedef for ppciPllMult. |

|

|

The memory controller memory types. |

|

|

The memory controller EDAC correction types. |

|

|

|

The memory controller EDAC scrub modes. |

|

|

Mutiprocessor semaphore state values. |

|

|

The PCI arbitration latency timeout values. |

|

|

The PCI data phase timeout values. |

|

|

PID input configuration values. |

|

|

PID output configuration values. |

|

|

CPU clock PLL multiplier values.

|

1.4.4

1.4.4