GLAST/LAT > DAQ and FSW > FSW > Doxygen Index > VXW / V7-0-3

Constituent: vxw_symbol Tag: rad750

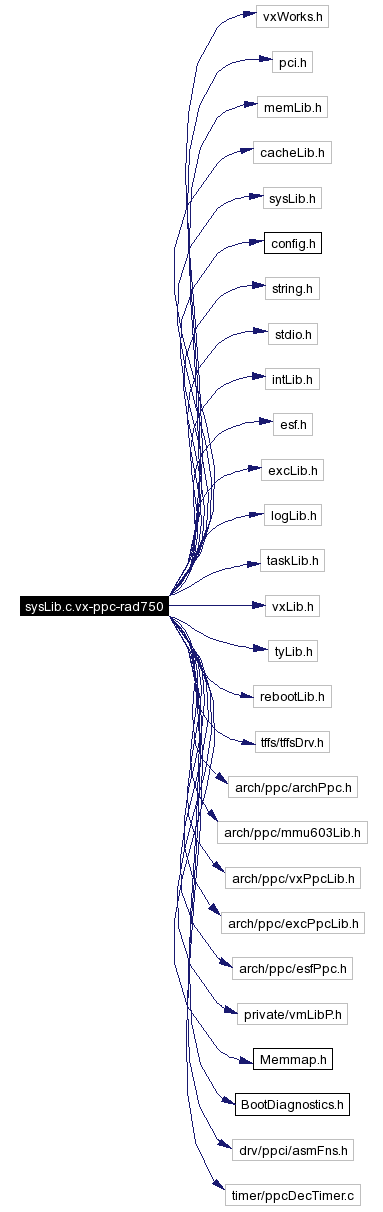

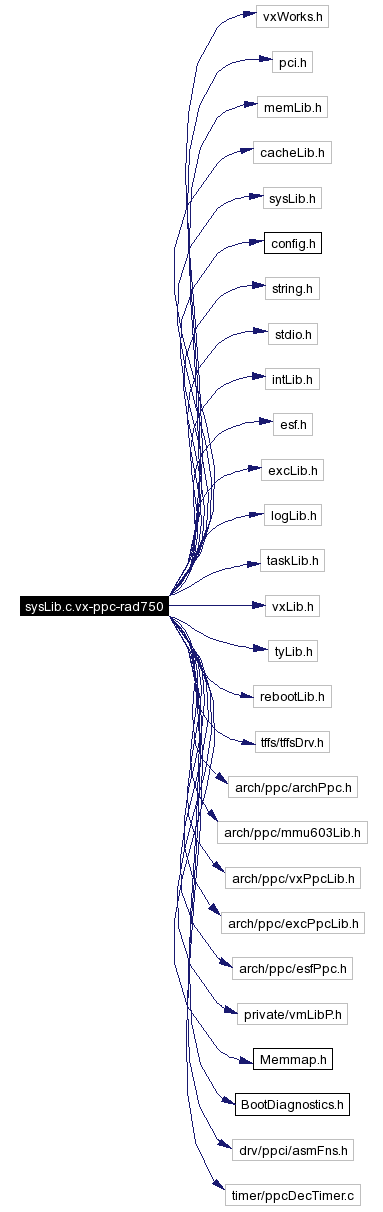

#include "vxWorks.h"

#include "pci.h"

#include "memLib.h"

#include "cacheLib.h"

#include "sysLib.h"

#include "config.h"

#include "string.h"

#include "stdio.h"

#include "intLib.h"

#include "esf.h"

#include "excLib.h"

#include "logLib.h"

#include "taskLib.h"

#include "vxLib.h"

#include "tyLib.h"

#include "rebootLib.h"

#include "tffs/tffsDrv.h"

#include "arch/ppc/archPpc.h"

#include "arch/ppc/mmu603Lib.h"

#include "arch/ppc/vxPpcLib.h"

#include "arch/ppc/excPpcLib.h"

#include "arch/ppc/esfPpc.h"

#include "private/vmLibP.h"

#include "Memmap.h"

#include "BootDiagnostics.h"

#include "drv/ppci/asmFns.h"

#include "timer/ppcDecTimer.c"

Include dependency graph for sysLib.c.vx-ppc-rad750:

Defines | |

| #define | BOOT_DIAGS_ADDR() ((BOOT_Diagnostics*) MEMMAP_BOOT_DIAGS_ADDR) |

| #define | WDOG_TIMEOUT_SECS 600 |

Functions | |

| LOCAL STATUS | connectPciInt (VOIDFUNCPTR *vector, VOIDFUNCPTR routine, int parameter) |

| LOCAL void | excHandler (int task, int vecNum, ESFPPC *pEsf) |

| char * | sysModel (void) |

| Return the model name of the CPU board. | |

| char * | sysBspRev (void) |

| Return the BSP version and revision number. | |

| BOOT_Diagnostics * | sysDiagsGet (void) |

| Return a pointer to the RAD750 boot diagnostics area. | |

| void | sysHwInit (void) |

| Initialize the system hardware. | |

| char * | sysPhysMemTop (void) |

| Get the address of the top of physical memory. | |

| char * | sysMemTop (void) |

| Get the address of the top of VxWorks memory. | |

| STATUS | sysToMonitor (int startType) |

| Transfer control to the ROM monitor. | |

| void | sysHwInit2 (void) |

| Initialize additional system hardware. | |

| int | sysProcNumGet (void) |

| Get the processor number. | |

| void | sysProcNumSet (int procNum) |

| set the processor number | |

| int | sysGetBusSpd (void) |

| Get the speed of the 60x processor bus. | |

| STATUS | sysLocalToPciAdrs (int adrsSpace, char *localAdrs, char **pBusAdrs) |

| Convert a local address to a PCI address. | |

| STATUS | sysPciToLocalAdrs (int adrsSpace, char *busAdrs, char **pLocalAdrs) |

| Convert a PCI address to a local address. | |

| STATUS | sysNvRamGet (char *string, int strLen, int offset) |

| Get the contents of non-volatile RAM. | |

| STATUS | sysNvRamSet (char *string, int strLen, int offset) |

| Write to non-volatile RAM. | |

Variables | |

| UINT32 | sysBatDesc [2 *(_MMU_NUM_IBAT+_MMU_NUM_DBAT)] |

| PHYS_MEM_DESC | sysPhysMemDesc [] |

| int | sysPhysMemDescNumEnt = NELEMENTS (sysPhysMemDesc) |

| int | sysCpu = CPU |

| int | sysProcNum |

| char * | sysBootLine = BOOT_LINE_ADRS |

| char * | sysExcMsg = EXC_MSG_ADRS |

| int | sysFlags |

| char | sysBootHost [BOOT_FIELD_LEN] |

| char | sysBootFile [BOOT_FIELD_LEN] |

| IMPORT STATUS(* | _func_intConnectRtn )(VOIDFUNCPTR *, VOIDFUNCPTR, int) |

| IMPORT int(* | _func_intEnableRtn )(int) |

| IMPORT int(* | _func_intDisableRtn )(int) |

| char | sysModelStr [] = "BAE SYSTEMS - RAD750" |

|

|

A macro to get the address of the boot diagnostics area |

|

|

The 10 minute watchdog timeout period, in terms of seconds. |

|

||||||||||||||||

|

This routine connects an ISR to a PCI interrupt line wired to a PPCI input PID. It is called indirectly when intConnect() is called. When SUPPORT_SHARED_PCI_INTERRUPTS is defined, there is another level of indirection as intConnect() calls pciIntConnect() which calls this routine. This indirection is set-up via _func_intConnectRtn and #PCI_INT_HANDLER_BIND.

|

|

||||||||||||||||

|

This routine is hooked into the standard VxWorks exception handling path (see excLib). In the case of a machine check exception, we clear the condition in the Power PCI bridge. For development configurations, VxWorks will suspend the task executing at the time the exception occured. For flight builds, the exception handler will store relevant information in the boot diagnostics region and reboot.

|

|

|

Return the BSP version and revision number. This routine returns a pointer to a BSP version and revision number, for example, 1.1/0. BSP_REV is concatenated to BSP_VERSION and returned.

|

|

|

Return a pointer to the RAD750 boot diagnostics area. This routine returns a pointer to the RAD750 boot diagnostics structure in SDRAM. This structure is used to pass information back and forth between the BSP and the PBC boot code.

|

|

|

Get the speed of the 60x processor bus. This routine returns the speed (in MHz) of the 60x system bus.

|

|

|

Initialize the system hardware. This routine initializes various features of the CPU board. It is called by usrInit() in usrConfig.c. This routine sets up the control registers and initializes various devices if they are present.

|

|

|

Initialize additional system hardware. This routine connects system interrupt vectors and configures any required features not configured by sysHwInit(). |

|

||||||||||||||||

|

Convert a local address to a PCI address. This routine returns the address of a local CPU memory resource as it would be seen on the PCI bus. The local address that is passed into this routine is the address of the local resource as seen by the CPU.

|

|

|

Get the address of the top of VxWorks memory. This routine returns a pointer to the first byte of memory not controlled or used by VxWorks. The user can reserve memory space by defining the macro SYS_MEM_TOP_ADRS in config.h. This routine returns the address of the reserved memory area. The value of SYS_MEM_TOP_ADRS is in first address of the reserved area. The system memory pool resides below this address.

|

|

|

Return the model name of the CPU board. This routine returns the model name of the CPU board. The returned string depends on the board model and CPU version being used, for example, "Motorola MTX - MPC 604e".

|

|

||||||||||||||||

|

Get the contents of non-volatile RAM. This routine copies the contents of non-volatile memory into a specified string. The string is terminated with an EOS.

|

|

||||||||||||||||

|

Write to non-volatile RAM. This routine copies a specified string into non-volatile RAM.

|

|

||||||||||||||||

|

Convert a PCI address to a local address. This routine returns a local address that is used to access the PCI bus. The bus address that is passed into this routine is the PCI bus address as it would be seen on the bus.

|

|

|

Get the address of the top of physical memory. This routine returns the address of the first missing byte of memory, which indicates the top of memory. Normally, the user specifies the amount of physical memory with the macro LOCAL_MEM_SIZE in config.h. BSPs that support run-time memory sizing do so only if the macro LOCAL_MEM_AUTOSIZE is defined. If not defined, then LOCAL_MEM_SIZE is assumed to be, and must be, the true size of physical memory.

|

|

|

Get the processor number. This routine returns the processor number for the CPU board, which is set with sysProcNumSet().

|

|

|

set the processor number This routine sets the processor number for the CPU board. Processor numbers should be unique on a single backplane. It also maps local resources onto the VMEbus.

|

|

|

Transfer control to the ROM monitor. This routine transfers control to the ROM monitor. Normally, it is called only by reboot()--which services ^X--and by bus errors at interrupt level. However, in some circumstances, the user may wish to introduce a startType value to enable special boot ROM facilities. The RAD750 version of sysToMonitor() makes sure that the boot diagnostics region is setup properly for the primary boot code, event when called from an internal VxWorks location.

|

|

|

Callback address for system interrupt connect function. |

|

|

Callback address for system interrupt disable function. |

|

|

Callback address for system interrupt enable function. |

|

|

sysBatDesc[] is used to initialize the block address translation (BAT) registers within the PowerPC 603/604/750 MMU. BAT hits take precedence over Page Table Entry (PTE) hits and are faster. Overlap of memory coverage by BATs and PTEs is permitted in cases where either the IBATs or the DBATs do not provide the necessary mapping (PTEs apply to both instruction AND data space, without distinction). The primary means of memory control for VxWorks is the MMU PTE support provided by vmLib and cacheLib. Use of BAT registers will conflict with vmLib support. User's may use BAT registers for i/o mapping and other purposes but are cautioned that conflicts with cacheing and mapping through vmLib may arise. Be aware that memory spaces mapped through a BAT are not mapped by a PTE and any vmLib() or cacheLib() operations on such areas will not be effective, nor will they report any error conditions. Note: BAT registers CANNOT be disabled - they are always active. For example, setting them all to zero will yield four identical data and instruction memory spaces starting at local address zero, each 128KB in size, and each set as write-back and cache-enabled. Hence, the BAT regs MUST be configured carefully. With this in mind, it is recommended that the BAT registers be used to map LARGE memory areas external to the processor if possible. If not possible, map sections of high RAM and/or PROM space where fine grained control of memory access is not needed. This has the beneficial effects of reducing PTE table size (8 bytes per 4k page) and increasing the speed of access to the largest possible memory space. Use the PTE table only for memory which needs fine grained (4KB pages) control or which is too small to be mapped by the BAT regs. The BAT configuration for 4xx/6xx-based PPC boards is as follows: All BATs point to PROM/FLASH memory so that end customer may configure them as required. [Ref: chapter 7, PowerPC Microprocessor Family: The Programming Environments] |

|

|

Name of file from which we booted. |

|

|

Name of host from which we booted. |

|

|

Address of boot line. |

|

|

System CPU type (e.g. PPC604). |

|

|

Catastrophic message area. |

|

|

Boot flags. |

|

|

String describing target board model. |

|

|

Initial value:

{

{

(void *) LOCAL_MEM_LOCAL_ADRS,

(void *) LOCAL_MEM_LOCAL_ADRS,

RAM_LOW_ADRS,

VM_STATE_MASK_VALID | VM_STATE_MASK_WRITABLE | VM_STATE_MASK_CACHEABLE |

VM_STATE_MASK_MEM_COHERENCY,

VM_STATE_VALID | VM_STATE_WRITABLE | VM_STATE_CACHEABLE |

VM_STATE_MEM_COHERENCY

},

{

(void *) RAM_LOW_ADRS,

(void *) RAM_LOW_ADRS,

LOCAL_MEM_SIZE - RAM_LOW_ADRS,

VM_STATE_MASK_VALID | VM_STATE_MASK_WRITABLE | VM_STATE_MASK_CACHEABLE |

VM_STATE_MASK_MEM_COHERENCY,

VM_STATE_VALID | VM_STATE_WRITABLE | VM_STATE_CACHEABLE |

VM_STATE_MEM_COHERENCY

}

}

Address translations for local RAM, is set here. PTEs are held, strangely enough, in a Page Table. Page Table sizes are integer powers of two based on amount of memory to be mapped and a minimum size of 64 kbytes. The MINIMUM recommended Page Table sizes for 32-bit PowerPCs are: Total mapped memory Page Table size ------------------- --------------- 8 Meg 64 K 16 Meg 128 K 32 Meg 256 K 64 Meg 512 K 128 Meg 1 Meg . . . . . . [Ref: chapter 7, PowerPC Microprocessor Family: The Programming Environments] |

|

|

The number of entries in the sysPhysMemDesc table. |

|

|

The processor number for this target. |

1.4.4

1.4.4