GLAST/LAT > DAQ and FSW > FSW > Doxygen Index > VXW / V7-0-3

Constituent: vxw_symbol Tag: rad750

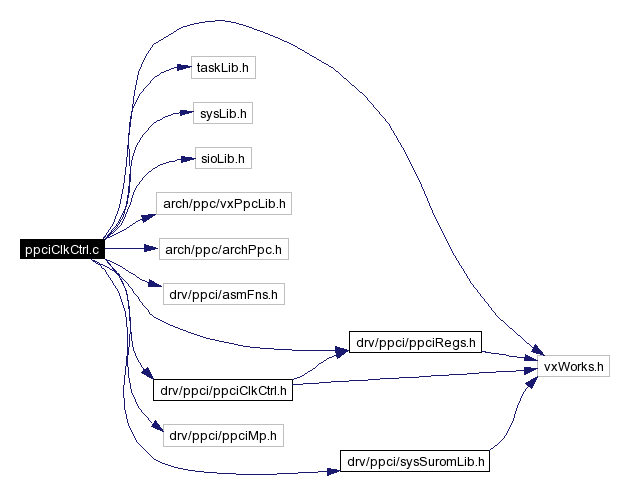

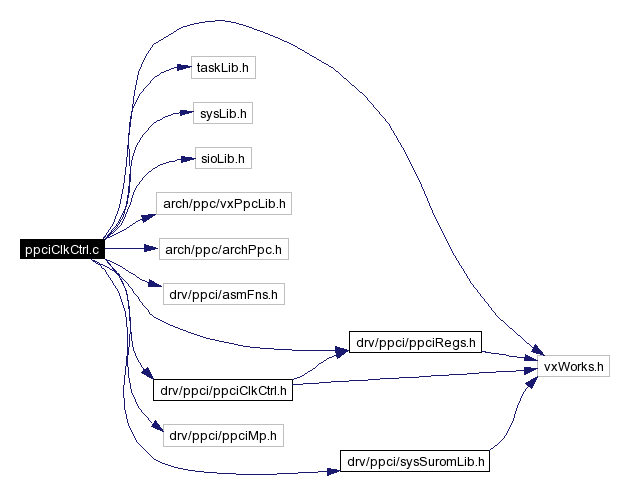

#include "vxWorks.h"

#include "taskLib.h"

#include "sysLib.h"

#include "sioLib.h"

#include "arch/ppc/vxPpcLib.h"

#include "arch/ppc/archPpc.h"

#include "drv/ppci/asmFns.h"

#include "drv/ppci/ppciRegs.h"

#include "drv/ppci/ppciClkCtrl.h"

#include "drv/ppci/ppciMp.h"

#include "drv/ppci/sysSuromLib.h"

Include dependency graph for ppciClkCtrl.c:

Defines | |

| #define | HID0_PWR_MODE_MASK 0x00E00000 |

| #define | HID0_SLEEP 0x00200000 |

| #define | HID0_NAP 0x00400000 |

| #define | HID0_DOZE 0x00800000 |

Functions | |

| int | getCpuClkDiv (void) |

| Get CPU Clock Divide. | |

| ppciPllMult_t | getCpuClkMult (void) |

| Get CPU Clock Multiplier. | |

| STATUS | setCpuClk (int divisor, ppciPllMult_t multiplier) |

| int | getRtcClkDiv (void) |

| Get RTC Clock Divide. | |

| STATUS | setRtcClkDiv (int value, BOOL recalibrate) |

| Set RTC Clock Divide. | |

| int | getPciClkDiv (void) |

| Get PCI Clock Divide. | |

| STATUS | setPciClkDiv (int value) |

| Set PCI Clock Divide. | |

| STATUS | setPowerMgtMode (pwrMgtMode_t cpuMode, pwrMgtMode_t bridgeMode) |

| Set Power Management Mode. | |

| static void | emcIsr (int junk) |

| int | getOscRate (void) |

| Return the CPU card oscillator rate. | |

| void | ppciClkCtrlInit (int rtcClkDiv, int osc, int minClk, int maxClk, int sigNum) |

| Init routine for Clock Control function. | |

Variables | |

| static int | oscRate |

| static int | minCpuClkForPll |

| static int | maxCpuClk |

| static int | emcWakeupSig |

-----------------------------------------------------------------------------

Description:

Clock control routines:

Restrictions:

Change History:

Date Pgm Description -------- --- ------------------------------------------------------ 14/04/00 DS Created.

-----------------------------------------------------------------------------

|

|

The PPC HID0 register doze power mode bit mask. |

|

|

The PPC HID0 register nap power mode bit mask. |

|

|

The PPC HID0 register power mode bit mask. |

|

|

The PPC HID0 register sleep power mode bit mask. |

|

|

EMC MP signal interrupt handler This external interrupt is used to wake up the CPU (from sleep mode), so there is nothing to do here.

|

|

|

Get CPU Clock Divide. Get CPU Clock Divide This routine returns the divide value being used to derive the CPU clock.

|

|

|

Get CPU Clock Multiplier. Get CPU Clock Multiplier This routine returns the encoded multiplier value used by the PLL logic to generate the CPU clock. Note that the value in HID1[0..3] is bit-reversed compare to this value.

|

|

|

Return the CPU card oscillator rate. Return the CPU card oscillator rate (defined in config.h).

|

|

|

Get PCI Clock Divide. Get PCI Clock Divide This routine returns the value being used to derive the PCI clock (by dividing the oscillator input): 1, 2, 4 or 8.

|

|

|

Get RTC Clock Divide. Get RTC Clock Divide This routine returns the value being used to derive the RTC (by dividing the oscillator input): 4, 8, 16 or 32.

|

|

||||||||||||||||||||||||

|

Init routine for Clock Control function. Init routine for Clock Control function This init routine is called by ppciInit (from sysHwInit) during system boot. Run-time constants and the RTC clock divide are set. Restrictions: Mutliprocessor signal support must be init before this call.

|

|

||||||||||||

|

Set CPU Clock This routine sets the divisor and multiplier values used to derive the CPU clock from the oscillator. The divisor is used in deriving the CPU clock from the oscillator input. The multiplier is used by the CPU's PLL.

|

|

|

Set PCI Clock Divide. Set PCI Clock Divide This routine sets the value to used to derive the PCI clock (by dividing the oscillator input).

|

|

||||||||||||

|

Set Power Management Mode. Set Power Management Mode This routine sets the power management mode of the CPU and the Power PCI bridge. Only the doze and full power modes are supported.

|

|

||||||||||||

|

Set RTC Clock Divide. Set RTC Clock Divide This routine sets the value to used to derive the RTC (by dividing the oscillator input). Changing this value affects the UART clock. If the recalibrate flag is set, SIO_BAUD_SET ioctl() is called keep the clock at its current rate. Note: it is possible to wire a board such that the RTC does not feed the UART clock. This configuration seems unlikely, but if it is, set recalibrate to FALSE.

|

|

|

The MP signal number used for EMC wakeup. |

|

|

The maximum CPU PLL setting. |

|

|

The minimum CPU PLL clock rate. |

|

|

The master oscillator rate. |

1.4.4

1.4.4