1.6. Memory Maps

For an SBC to communicate with other PCI modules requires the mapping of several memory spaces over the PCI bus.

1.6.2. LCB and SBC Memory Maps

The LCB exposes its I/O space and Memory space to every SBC in the crate. In turn each SBC exposes some fraction of its physical memory to the LCB for DMA, including memory for event data, export lists and result lists.

1.6.2.1. LCB Exposed Memory

The LCB exposes its I/O space and Memory space to every SBC in the crate. The I/O space allows the SBC and LCB to coordinate event memory usage. The Memory space allows the SBC and LCB to coordinate export and result lists. See [2] for more details.

The PCI addresses of the I/O and Memory spaces is located in the BARs of the LCB. Both memory spaces must be mapped on a 32-bit boundry.

Sample memory maps for the I/O and Memory spaces of a LCB are shown below in Figure 1-1 and Figure 1-2 . The PCI addresses are for illustrative purposes only, as the actual addresses will be assigned by the Director SBC at system start.

The mapping from PCI space to local address is handled by the PCI-host bridge of the SBC and/or memory controller. As the flight board is not yet determined the exact method for mapping memory is not currently known.

1.6.2.1.1. NRL Board Memory Mapping Details

The "NRL Board" uses a DMA engine to access the three types of PCI memory spaces. Programming the registers of the DMA engine allows access to the PCI Configuration, I/O and Memory spaces.

The registers of the DMA engine are located in the local memory space of the SBC at address 0x8000_0000.

The "NRL Board" does not use memory-mapped I/O to access the PCI memory spaces.

See [8] for more details.

1.6.2.2. SBC Exposed Memory

Each SBC exposes three logical memory spaces to the DMA engine of the LCB – Event memory, Export List memory and Result List memory.

A SBC can only have one event memory space, but can have multiple export and result lists. The size, memory alignment and I/O operations for each space is shown below in Table 1-1.

| Memory Space | LCB DMA | Size | Alignment |

|---|---|---|---|

| Event | Write | 640 KB | 1 MB |

| Export List | Read | 4092 Bytes per List | 512 Byte |

| Result List | Write | 4084 Bytes per List | 8 Byte |

Table 1-1. SBC DMA spaces

As shown in Table 1-1 the LCB DMA engine writes to the event memory space, reads from the export list space and writes to result list space.

The mapping from PCI space to local address is handled by the PCI-host bridge of the SBC and/or memory controller. As the flight board is not yet determined the exact method for mapping memory is not currently known.

1.6.2.2.1. NRL Board Memory Mapping Details

The "NRL Board" can map 8MB of SRAM to the PCI address space. The 8MB block begins at local address 0x4000_0000. See [8] for more details.

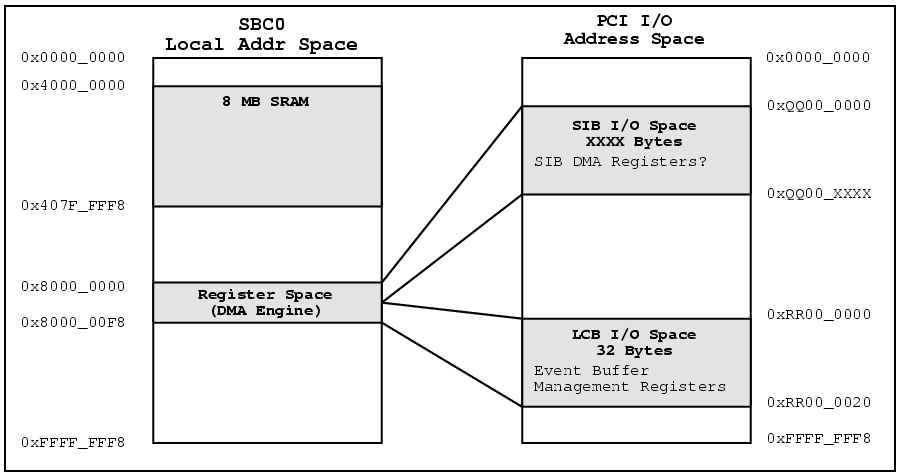

Figure 1-3 below shows an example PCI I/O Space memory map for the "NRL Board" configured as the Director SBC. The PCI addresses shown are for illustrative purposes only.

Note the Director SBC has access to the PCI I/O Space for both the SIB and LCB. An Actor SBC, on the other hand, would only have access to the PCI I/O Space of the LCB.

Figure 1-4 below shows an example PCI Memory Space memory map for the "NRL Board" configured as the Director SBC. The PCI addresses shown are for illustrative purposes only.

Note the Director SBC has access to the PCI Memory Space for both the SIB and LCB. An Actor SBC, on the other hand, would only have access to the PCI Memory Space of the LCB.

1.6.2.3. Putting It All Together

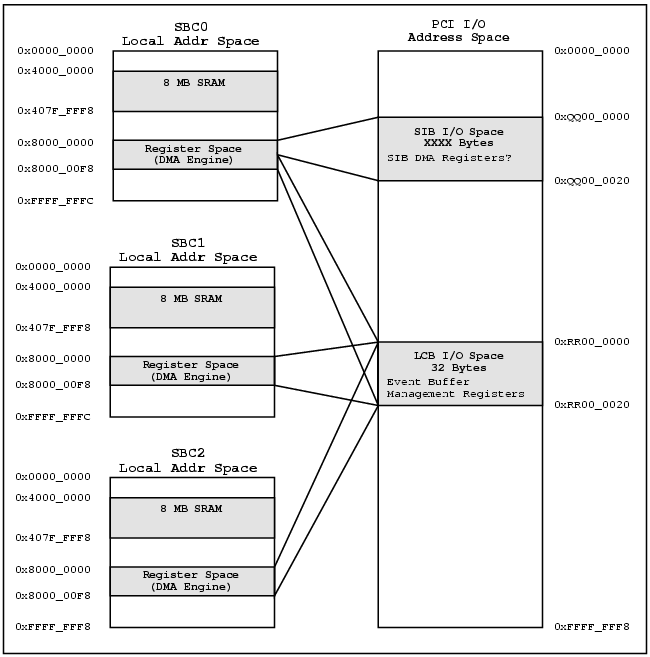

Figure 1-5 below is a sample PCI I/O Space Memory Map for an entire PCI crate, including three SBCs, a LCB and a SIB. The SBCs are assumed to be "NRL Board"s. The PCI addresses shown are for illustrative purposes only.

Note the Director SBC has access to the PCI I/O Space for both the SIB and LCB. The Actor SBCs, on the other hand, only have access to the PCI I/O Space of the LCB.

Figure 1-6 below is a sample PCI Memory Space Memory Map for an entire PCI crate, including three SBCs, a LCB and a SIB. The SBCs are assumed to be "NRL Board"s. The PCI addresses shown are for illustrative purposes only.

Note the Director SBC has access to the PCI Memory Space for both the SIB and LCB. The Actor SBCs, on the other hand, only have access to the PCI Memory Space of the LCB.